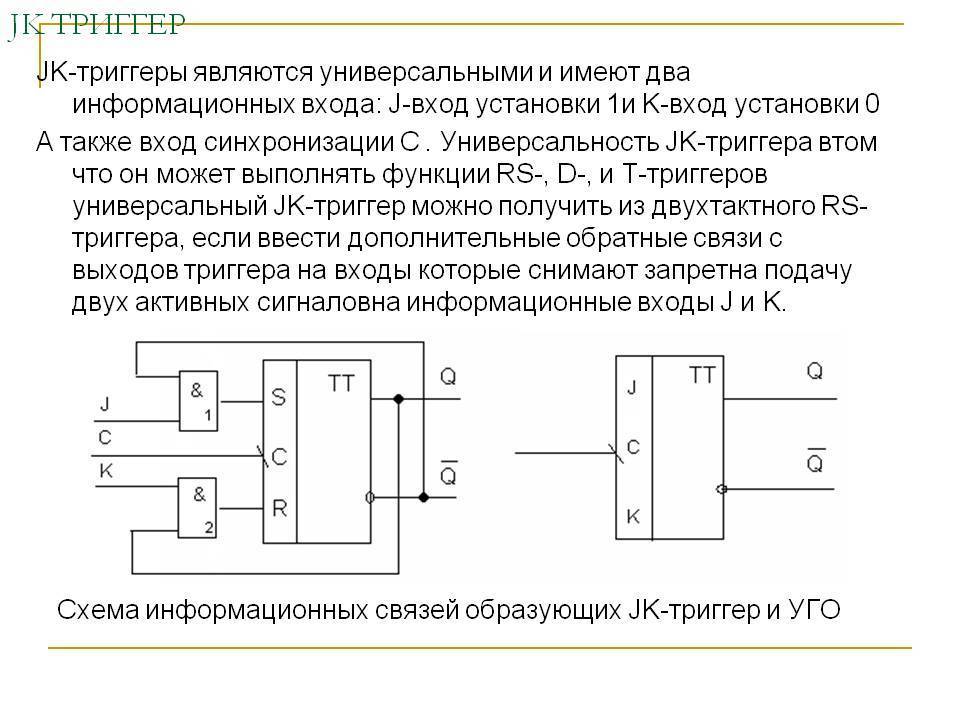

JK триггер

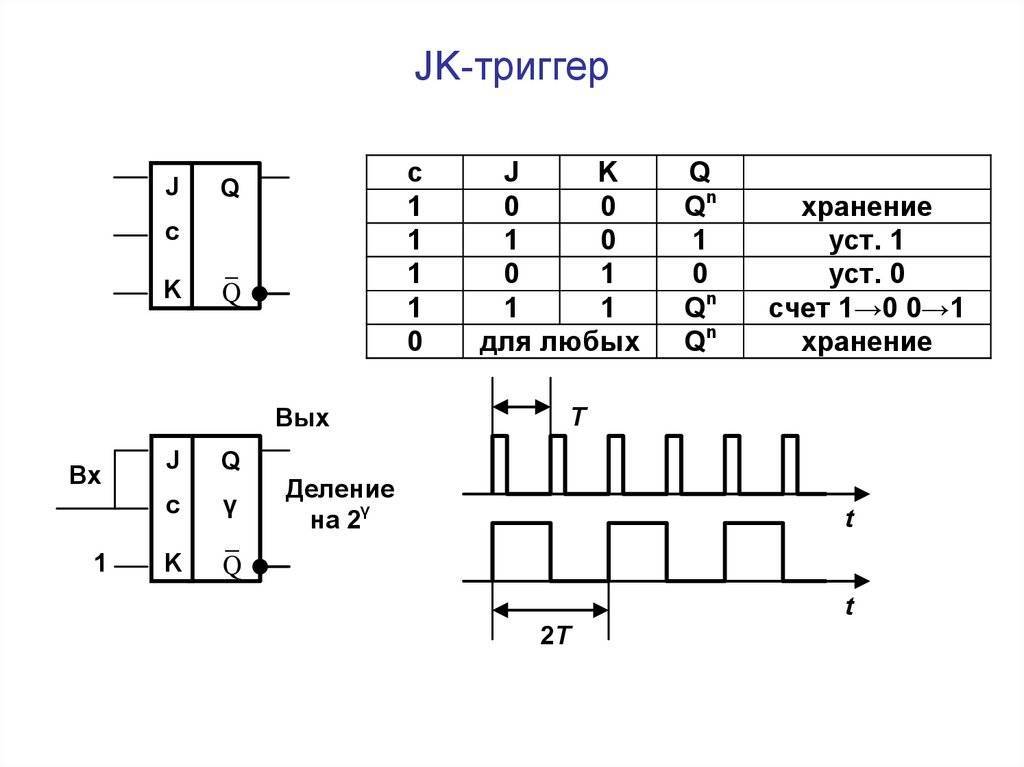

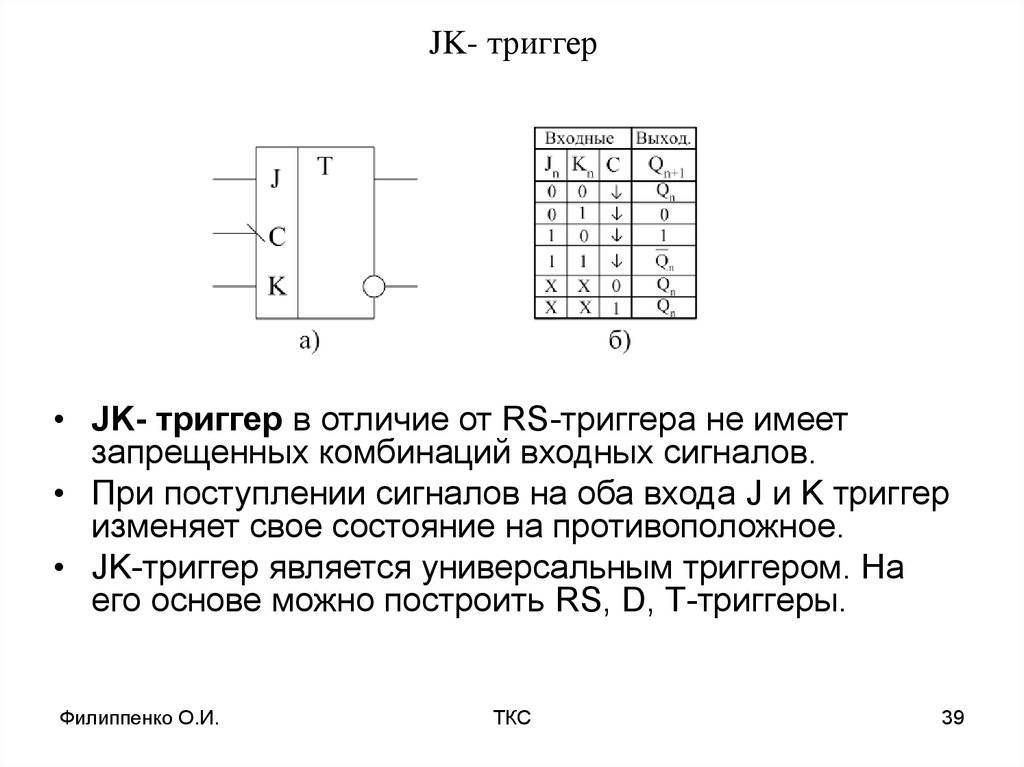

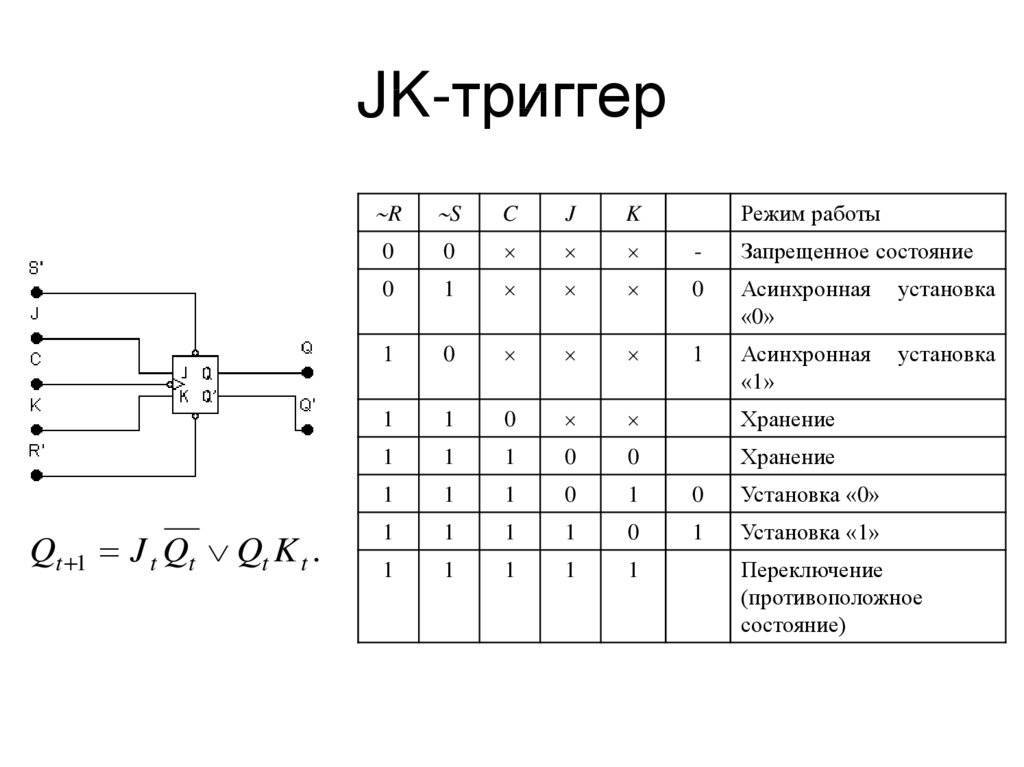

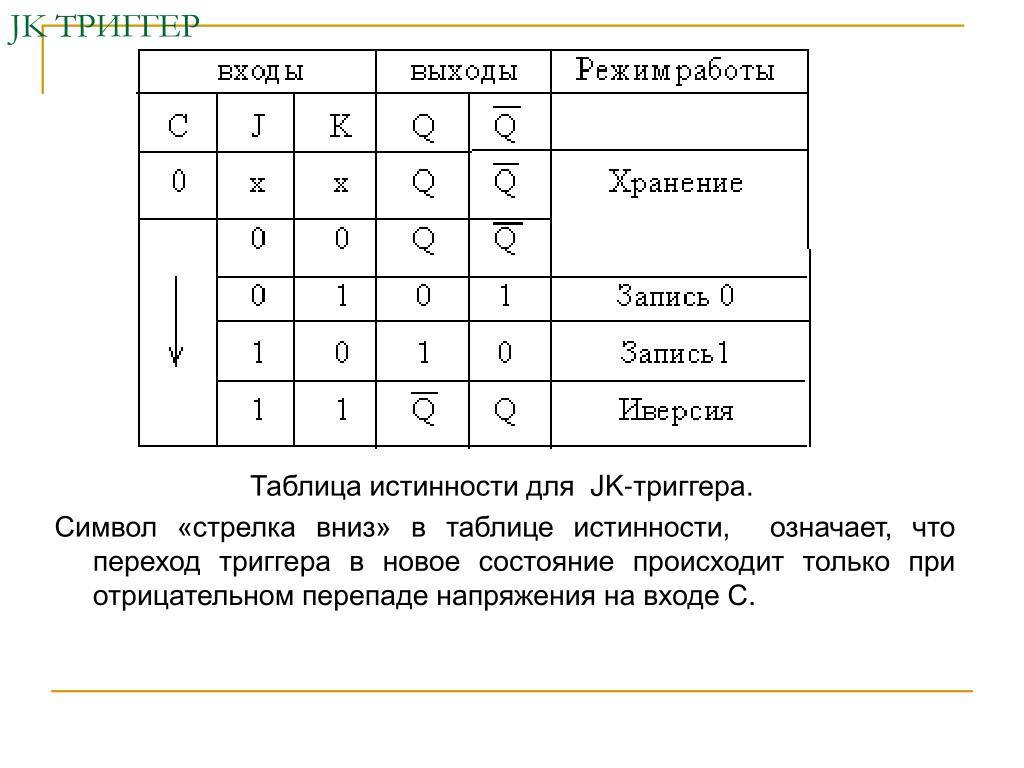

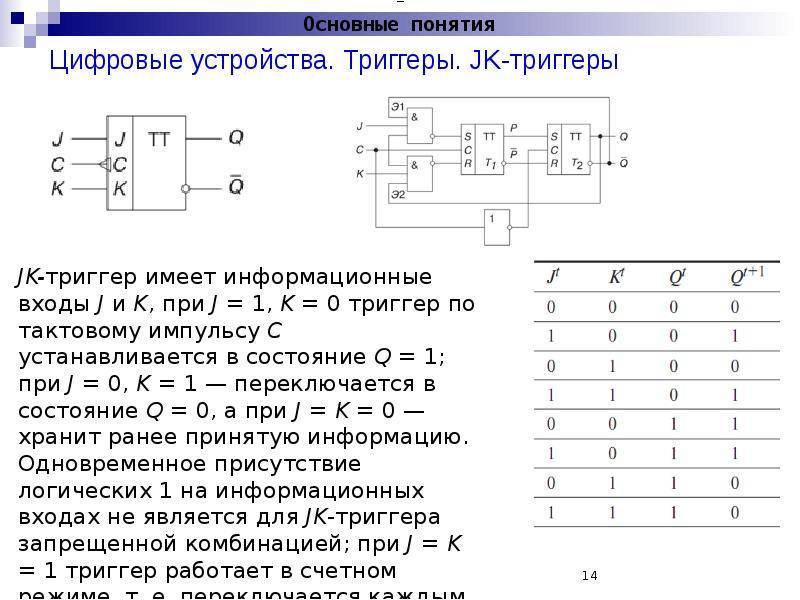

Микросхема типа К555ТВ9, является представителем семейства JK триггеров, который имеет следующий принцип работы.

Обозначение JK триггера К555ТВ9.

Микросхема К555ТВ9 содержит два JK триггера. Триггеры данного типа сложнее по устройству и по управлению по сравнению с RS триггером. В дополнение к стандартным входам R и S, которые работают аналогично с RS триггером, в JK триггере имеются информационные входа J и K, а также вход синхронизации С.

| Входы | Выходы | |||||

| -S | -R | C | J | K | Q | -Q |

| 1 | Х | Х | Х | 1 | ||

| 1 | Х | Х | Х | 1 | ||

| Х | Х | Х | Не определено | |||

| 1 | 1 | 1→0 | 1 | 1 | ||

| 1 | 1 | 1→0 | 1 | 1 | ||

| 1 | 1 | 1→0 | Не изменяется | |||

| 1 | 1 | 1→0 | 1 | 1 | Меняется напротивоположное | |

| 1 | 1 | 1 | Х | Х | Не изменяется | |

| 1 | 1 | Х | Х | Не изменяется | ||

| 1 | 1 | 0→1 | Х | Х | Не изменяется |

Принцип работы JK триггера следующий. Вход R триггера служит для перевода прямого выхода в лог.1, а вход S триггера – в состояние лог.0. Вход С (англ. Clock – часы)служит для тактирования JK триггера, то есть все изменения выходов происходят только когда на входе С сигнал изменяется с высокого уровня на низкий. Информационные входа J (англ. Jump – прыжок) и К (англ. Kill – убить) работают следующим образом: если на J лог.1 и на К лог.0, то по импульсу со входа С на Q будет лог.1 и на –Q будет лог.0. Для изменения уровня сигнала на выходах на противоположные необходимо на J подать лог.0, а на К лог.1, тогда по импульсу на входе С состояние выходов измениться.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

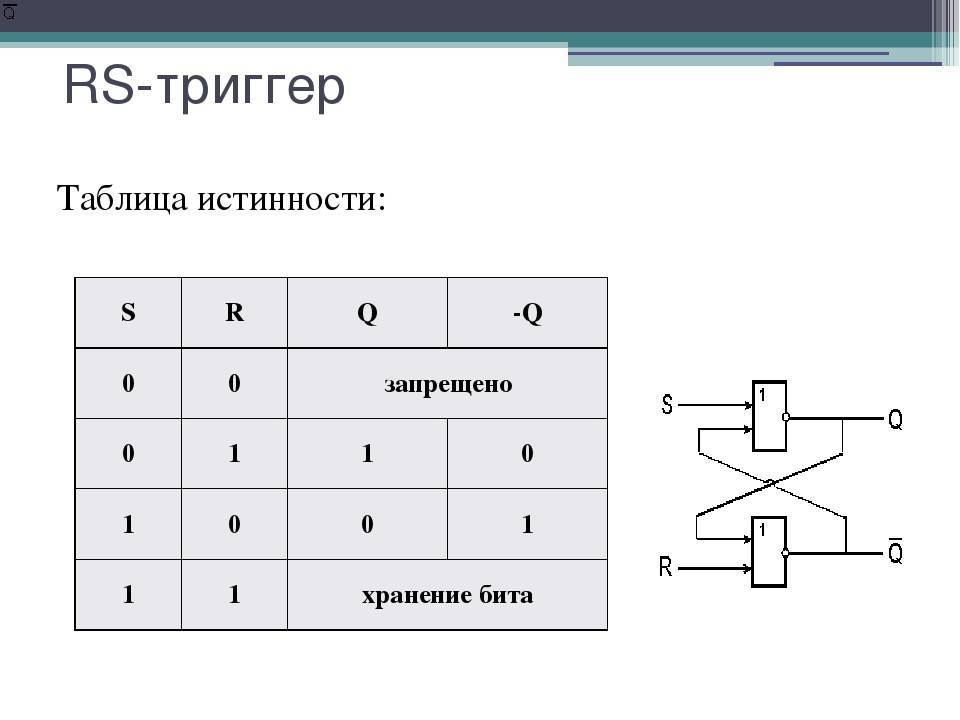

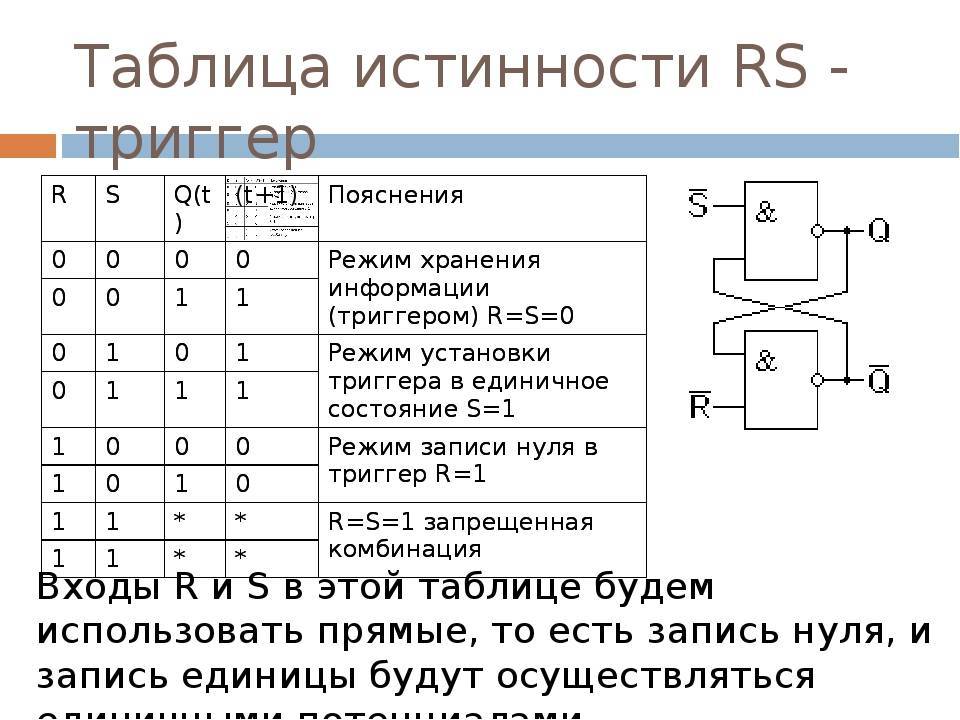

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно Что такое электрическое поле: объяснение простыми словам

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

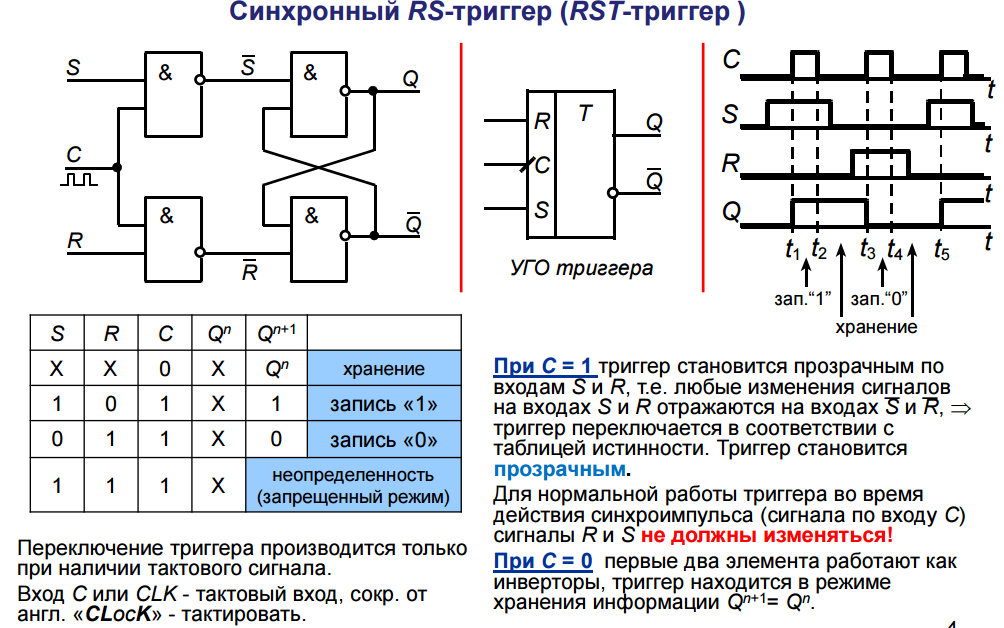

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Возможности

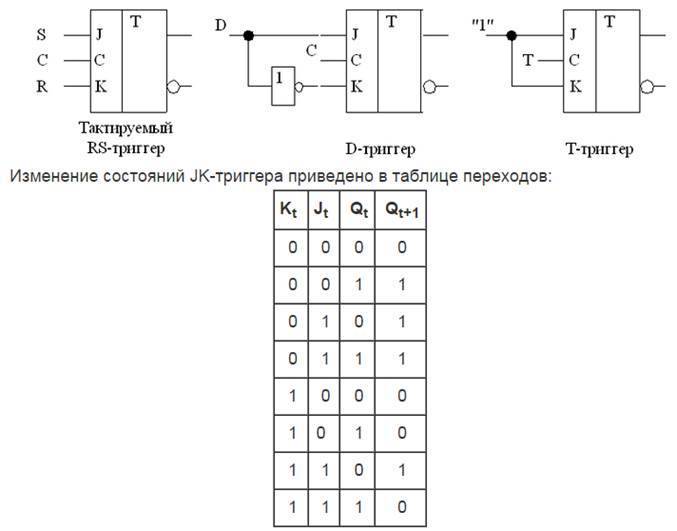

Также важным отличием данных моделей является то, что в них устранена неопределенность, которая может возникнуть в случае, если входные сигналы будут поданы в определённой комбинации. Также существенным преимуществом является тот факт, что они могут выполнять функционал T-, D- и RS-триггеров. Комбинированный тип имеет дополнительные асинхронные входы, которые используются для предварительной установки приборов в определённое состояние. Примитивный JK можно получить из RS, у которого есть динамическое управление. Для этого необходимо его дополнить обратными связями с выходов на входы. Для получения Т-триггера необходимо на входы подать уровень напряжения, который установит логическую единицу.

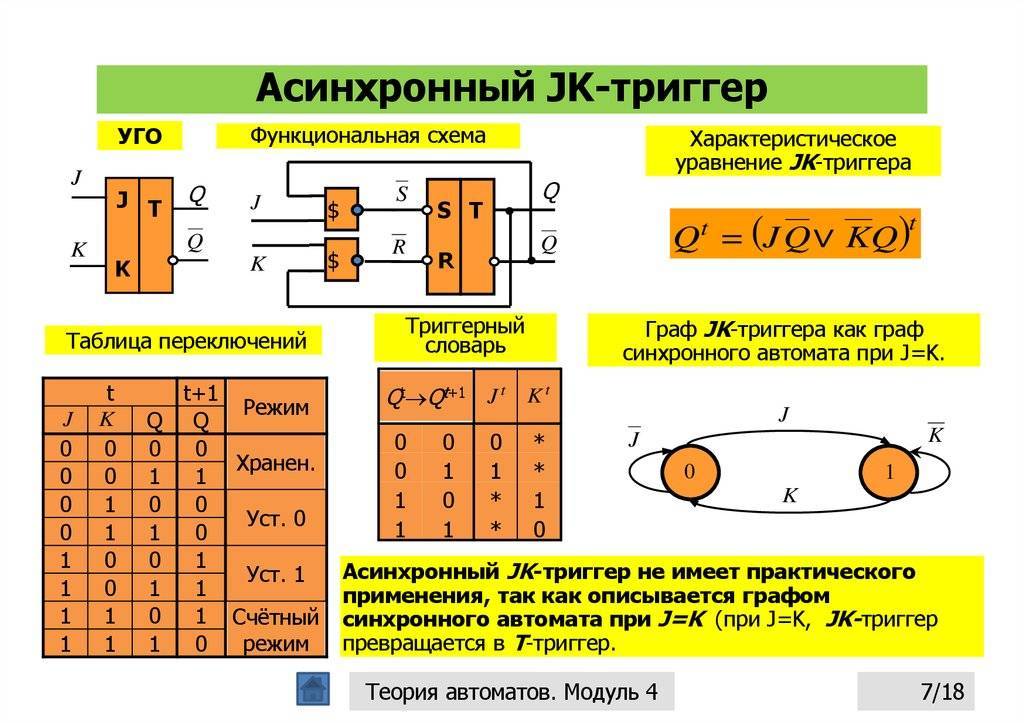

В каких состояниях может быть главный герой статьи? Существует два принципа действий: асинхронный и синхронный. Во время первого происходит обмен данных независимо от входов. Синхронный JK-триггер действует одновременно, и из-за требований он является основным используемым элементом.

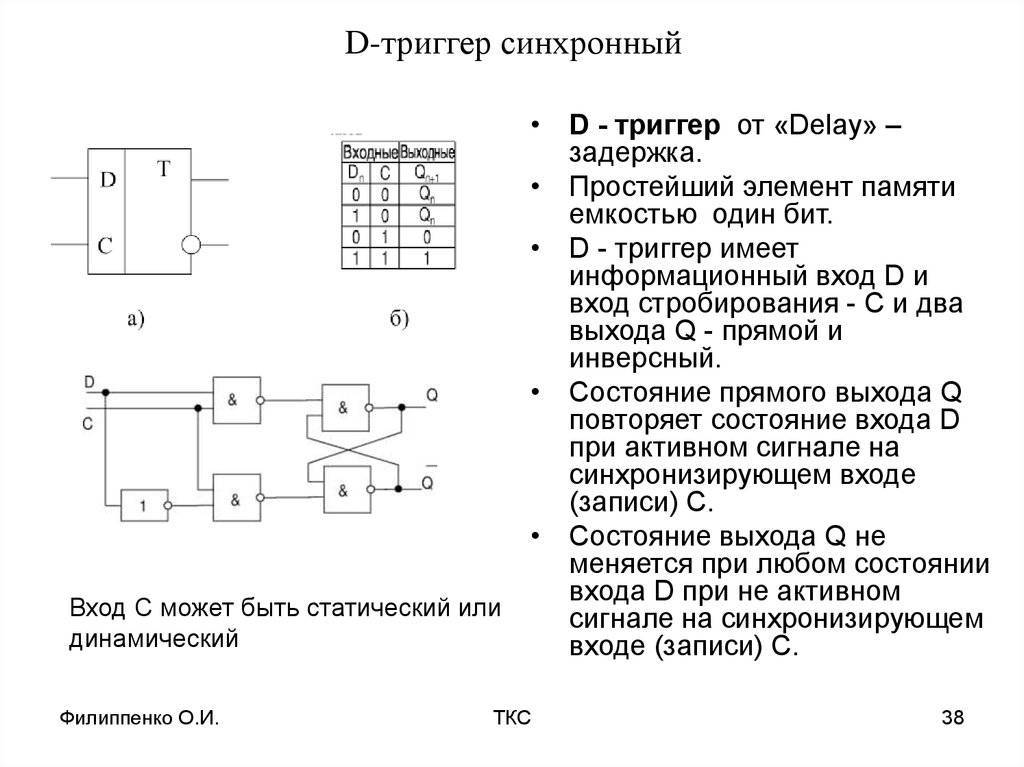

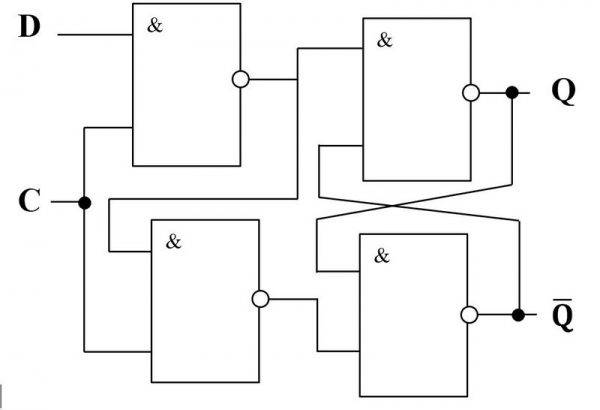

Схема реализации d-триггера

Реализация д-тригера может выполняться на основе ТТЛ (транзисторно-транзисторная логика) элементов, а также логических элементах КМОП.

Большинство микросхем относятся к компонентам с комплиментарной структурой – металл-оксид-полупроводник (КМОП). Данная технология основывается на использовании полевых транзисторов с изолированными затворами.

Реализация д-триггера на ТТЛ элементах приведена на рисунке ниже.

Схема устройства на ТТЛ-элементах

Если в логическом элементе D-вход соединить с инверсным выходом, то в этом случае прибор можно использовать в качестве счётного или Т-триггера. В этом случае при подаче импульса на С-вход логический компонент переходит в противоположное положение.

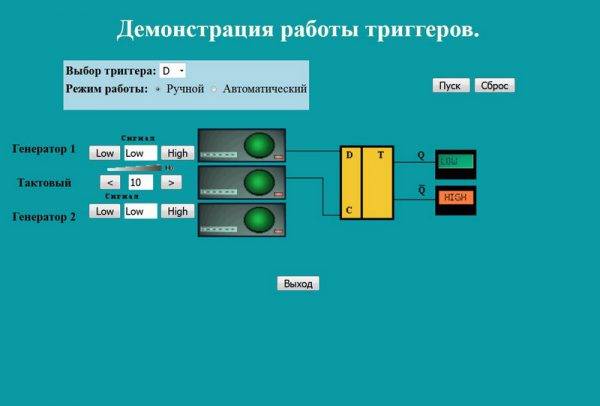

В сети интернет имеются сайты с сервисами, на которых можно просмотреть результат работы разного вида триггеров. Тип устройства выбирается из соответствующего списка.

Демонстрация работы устройств

Триггеры являются важной компонентой для создания различных микросхем. Их использование позволяет выполнять устройства с цифровой памятью

В микропроцессорной технике они являются основой для реализации электронных компонентов оперативной памяти. Их используют в регистрах сдвига и регистрах хранения.

Логические вентили(логические элементы).

Процессы, необходимые для функционирования любых технологических устройств ( в т. ч. и ПК)

можно реализовать с помощью ограниченного набора логических элементов.

Буфер.

Буфер, представляет из себя усилитель тока, служащий для согласования различных логических

вентилей, в особенности имеющих в своей основе разную элементную базу (ттл или КМОП).

Элемент, служащий для инвертирования поступающих сигналов – логическая еденица превращается

в ноль, и наоборот.

Логическая схема И.

И – элемент логического умножения. Еденица (высокий уровень напряжения) на выходе, появляется

только в случае присутствия едениц, на обоих входах, одновременно.

Пример применения элемента И в реальном техническом устройстве: По тех. заданию, механический пресс должен срабатывать, только при одновременном нажатии

двух кнопок, разнесенных на некоторое расстояние. Смысл тех. задания заключается в том, что бы обе

руки оператора были заняты на момент хода пресса, что исключило бы возможность случайного

травмирования конечности.

Это может быть реализовано как раз, с помощью логического элемента И.

Логическая схема И – НЕ.

И-НЕ – наиболее часто используемый элемент. Он состоит из логических вентилей И и НЕ, подключенных

последовательно.

Логическая схема ИЛИ.

ИЛИ – схема логического сложения. Логическая еденица на выходе, появляется в случае присутствия

высокого уровня(еденицы) на любом из входов.

Логическая схема ИЛИ – НЕ.

ИЛИ – НЕ состоит из логических элементов ИЛИ и НЕ, подключеных последовательно.

Соответственно, НЕ инвертирует значения на выходе ИЛИ.

Логическая схема исключающее ИЛИ.

Этот вентиль выдает на выходе логическую еденицу, если на одном из входов

– еденица, а на другом, ноль.

Если на входах присутствуют одинаковые значения – на выходе ноль.

Триггер Шмитта.

Триггер Шмитта выдает импульс правильной формы, при сигнале произвольной формы на входе.

Применяется для преобразования медленно меняющихся сигналов в импульсы, с четко очерчеными

краями.

Классификация

Если стандартные логические элементы являются строительными блоками комбинационных схем, бистабильные схемы, включая и RS-триггер, являются основными компонентами построения последовательностных логических устройств, таких, как регистры хранения данных, регистры сдвига, устройства памяти или счетчики. В любом случае рассматриваемые триггеры (разумеется, как и все последовательностные схемы) могут быть выполнены в виде следующих основных типов:

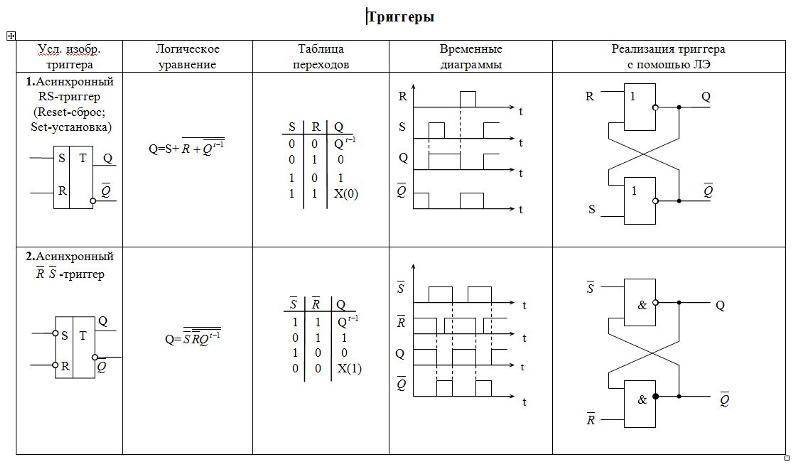

1. Асинхронный RS-триггер – схема, которая изменяет состояние сразу при изменении входных сигналов. Для рассматриваемого типа устройств ими являются сигналы на информационных входах R (сброс) и S (установка). Согласно установившейся практике, соответствующие входы называют так же, как и сигналы на них.

2. Синхронный RS-триггер, управляемый статически, работа которого синхронизирована с уровнем определенного тактового сигнала.

3. Триггер по п.2 с динамическим управлением, работа которого синхронизирована с моментами появления фронтов (или спадов) тактового сигнала.

Таким образом, если изменения состояния выходов происходят только при наличии тактового сигнала, который подается на отдельный тактовый вход C, то триггер является синхронным. В противном случае схема считается асинхронной. Чтобы сохранить свое текущее состояние, последовательностные схемы используют обратную связь, т. е. передачу части выходного сигнала на ее вход.

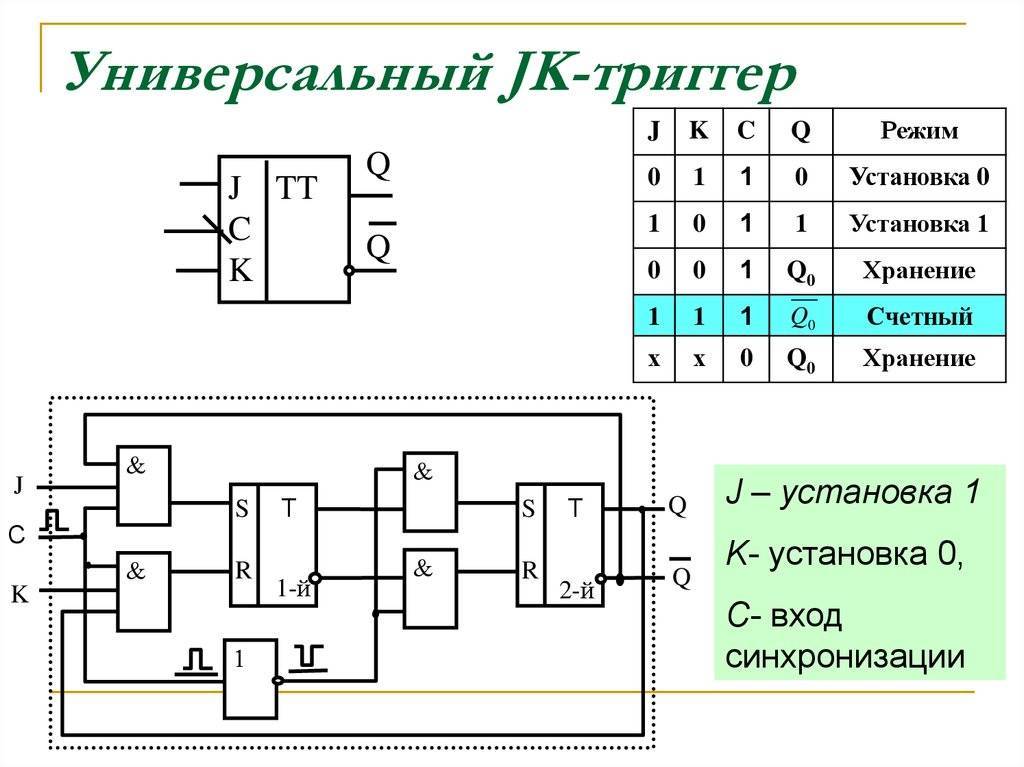

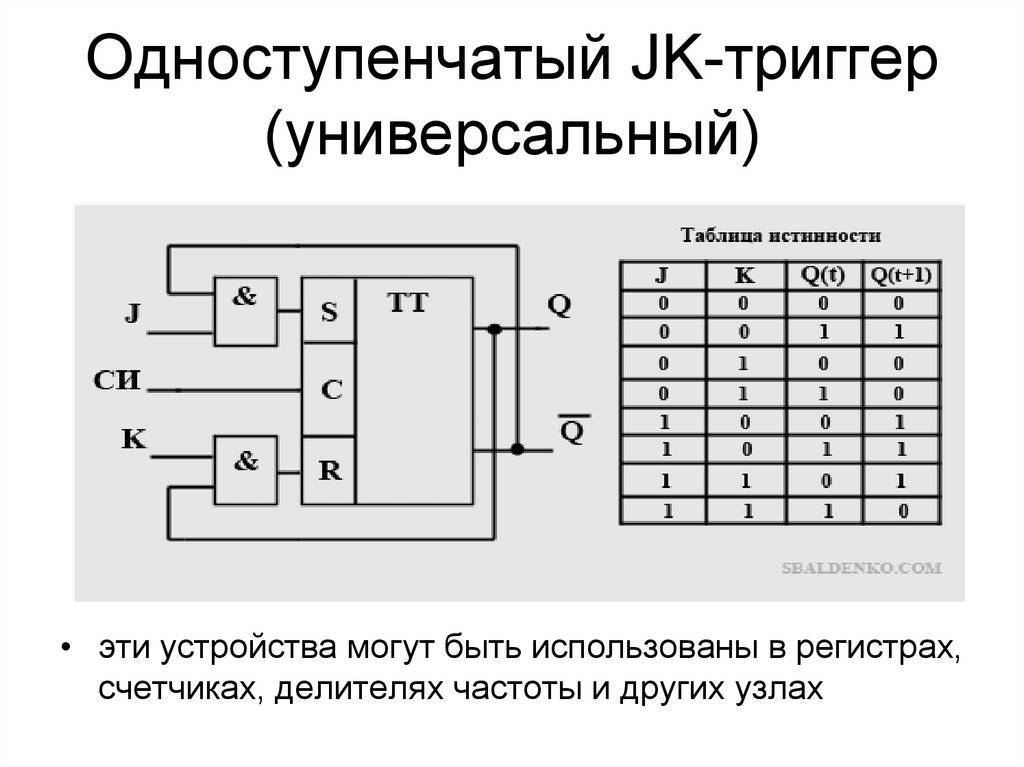

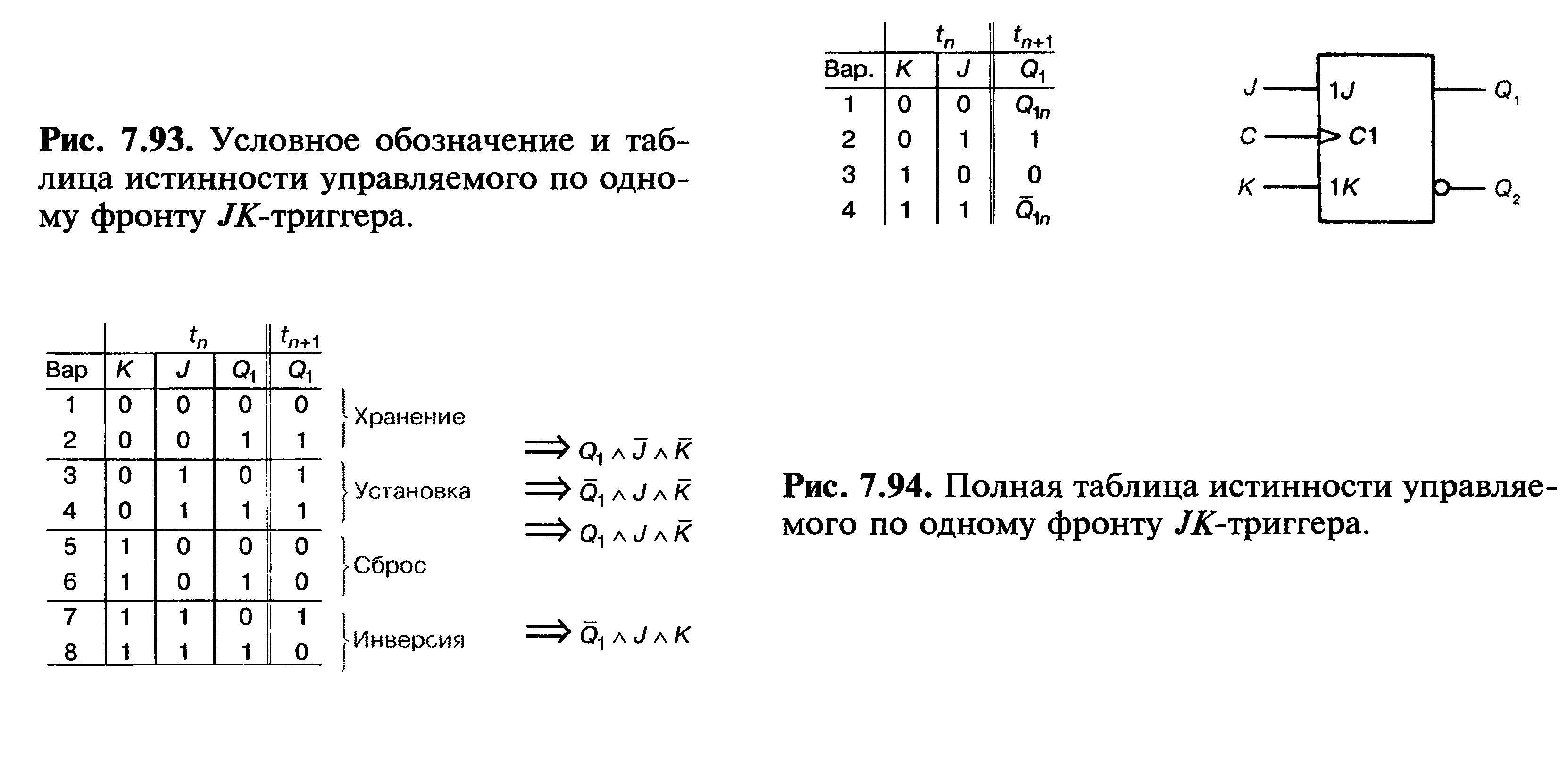

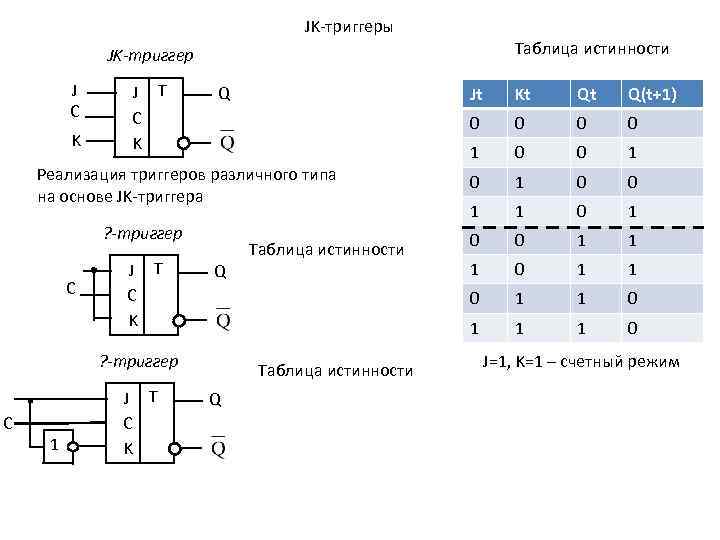

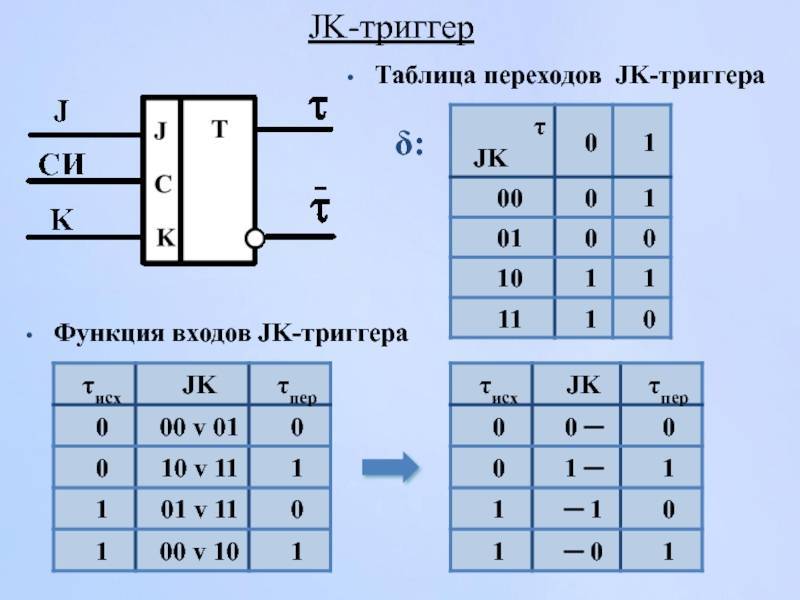

Синхронный JK-триггер

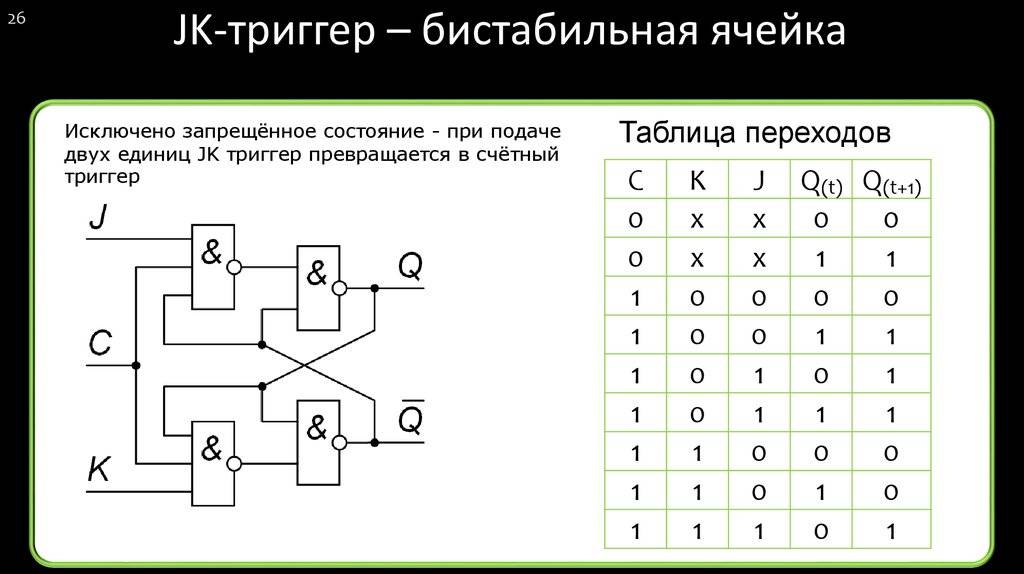

Основное преимущество данного триггера – у него нет запрещенного состояния.

Рис. 3.1. Условное обозначение синхронного JK-триггера.

Логика работы:

- C=1

- J=0 K=1 Q(t+1)=0

- J=0 K=0 Q(t+1)=Q(t)

- J=1 K=0 Q(t+1)=1

- J=1 K=1 Q(t+1)=no Q(t)

- C=0 – режим хранения

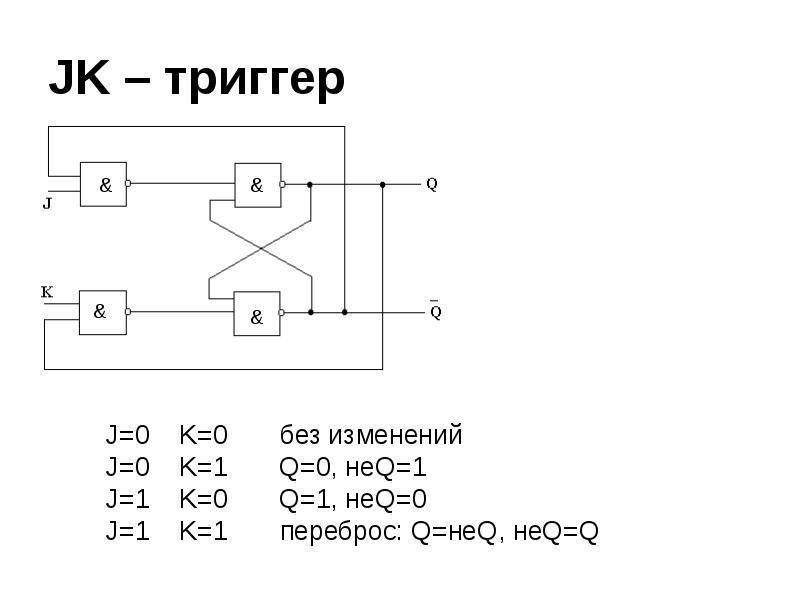

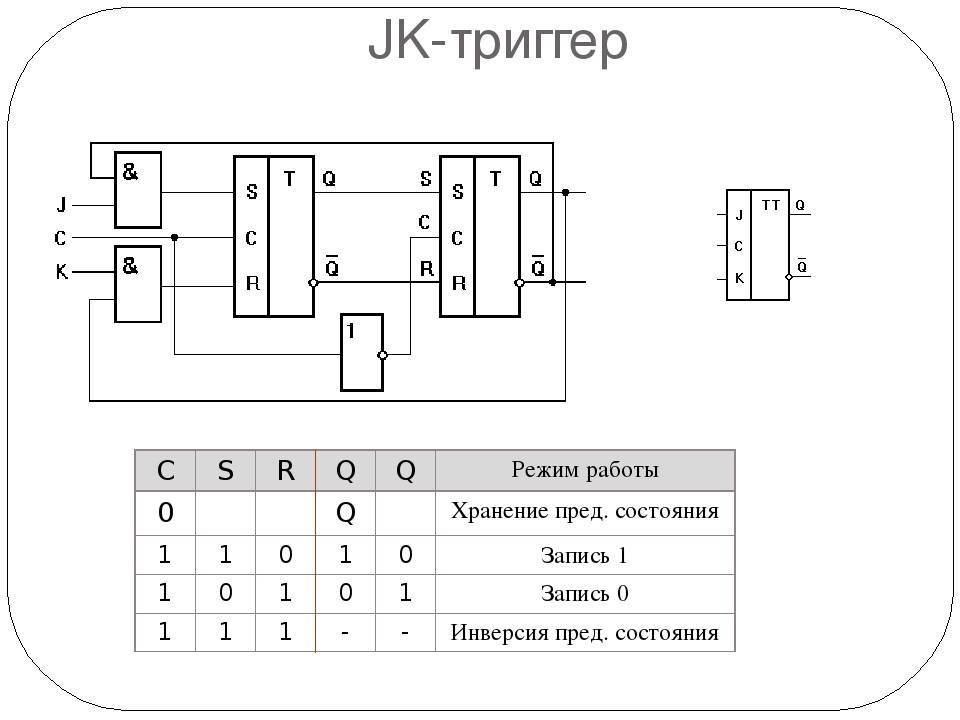

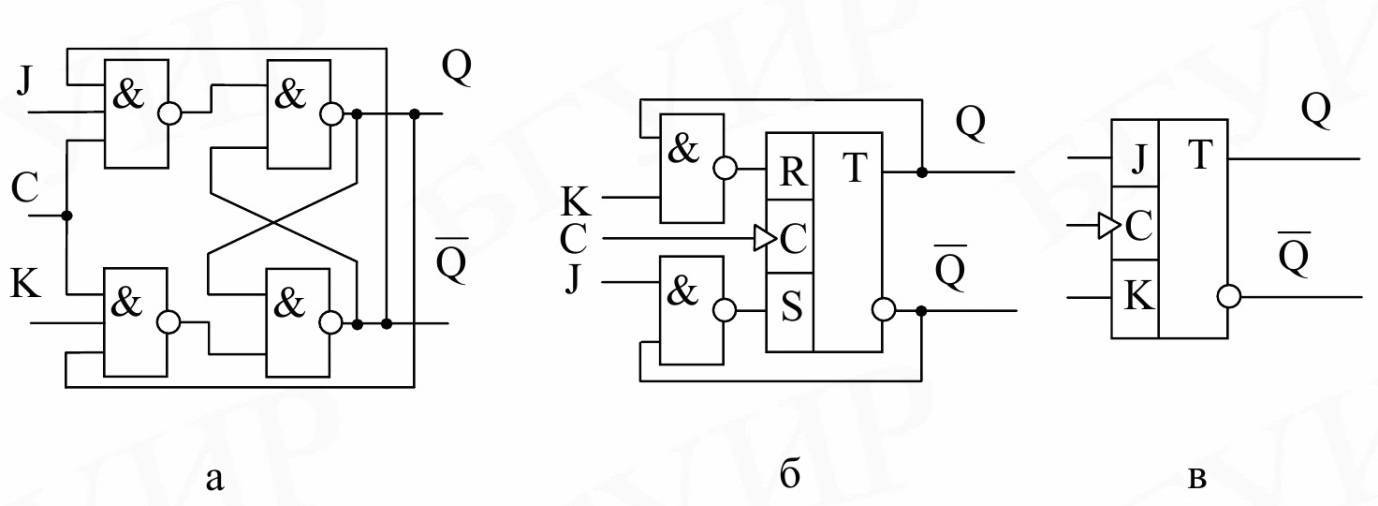

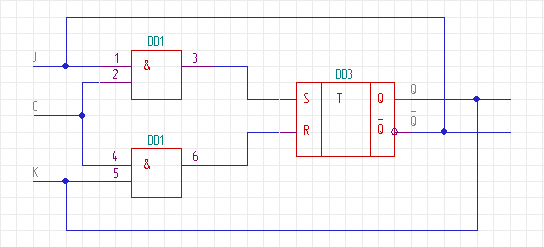

Схема JK-триггера

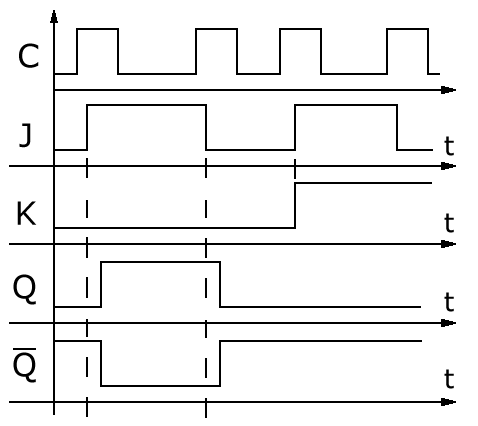

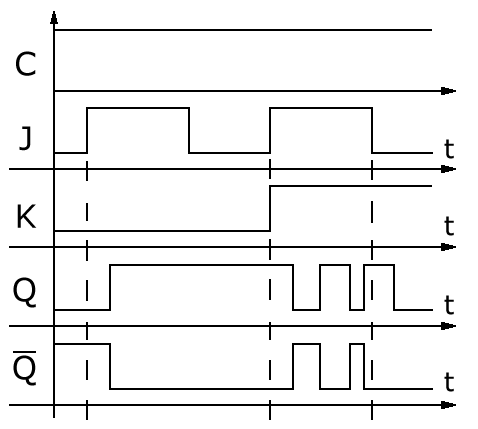

Рис. 3.2. Схема JK-триггера и временные диаграммы его работы.

Рис. 3.3. Временные диаграммы.

Считается, что значения на выходе изменяются одновременно. Записать в триггер можно только изменяющееся значение, хранимое в триггере значение – нельзя.

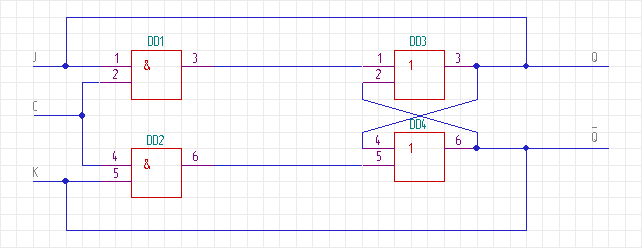

Конкретная реализация синхронного JK-триггера

Рис. 3.4. Конкретная реализация JK-триггера и временные диаграммы его работы.

Рис. 3.5. Временные диаграммы.

Если длительность управляющих сигналов больше времени переключения триггера – получаем автоколебательный режим (при наличии двух единиц на входах).

При J=K=1{\displaystyle J=K=1\,\!} необходимо подать на вход сихронизирующий импульс, не превышая время переключения (время ПП) внутри JK-триггера.

tJK=2tNOR+tAND{\displaystyle t_{JK}=2t_{NOR}+t_{AND}\,\!}

Окончание автоколебательного процесса определяется длительностью сигнала синхронизации и времени установки триггера.

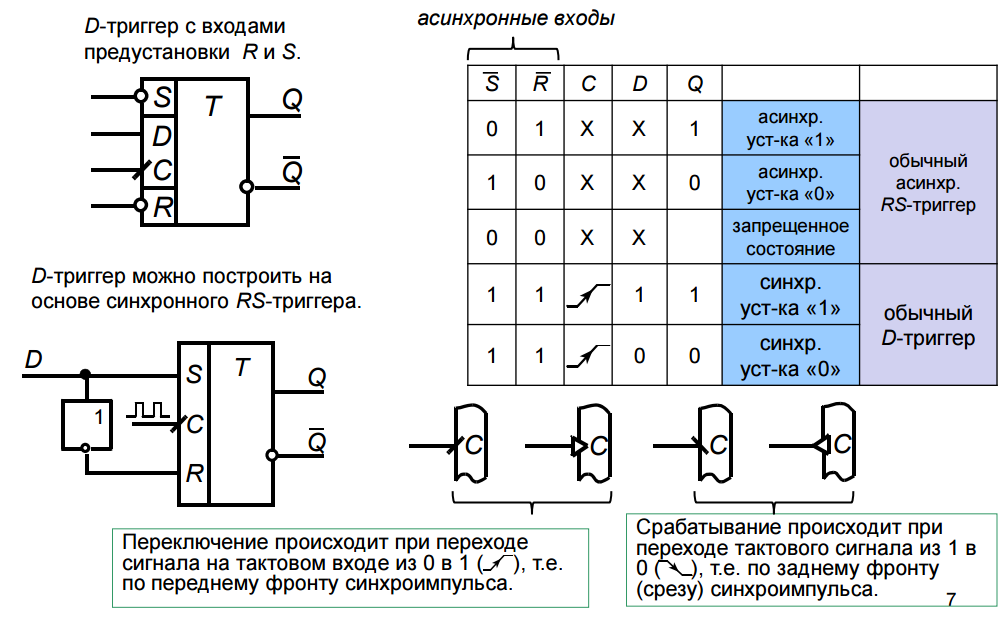

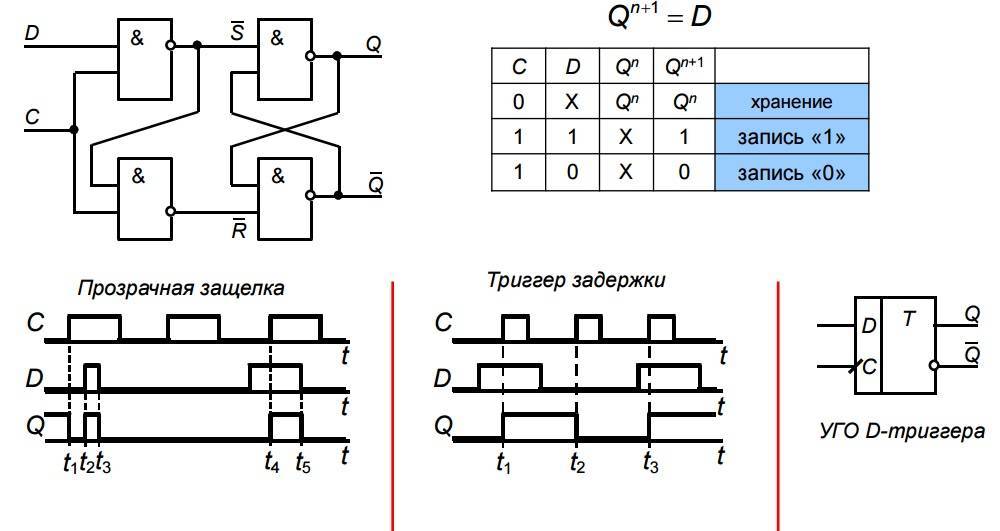

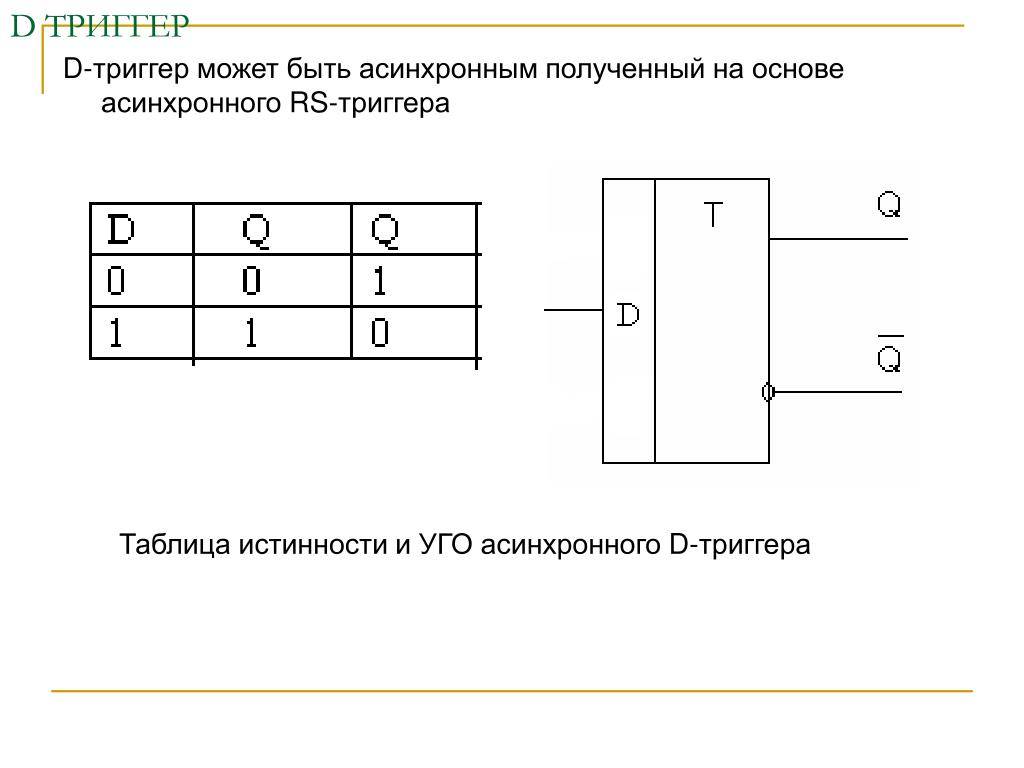

D-триггер

D-триггер (от англ. delay) запоминает входную информацию при поступлении синхроимпульса.

Хранение информации в D-триггерах обеспечивается за счет синхронизации, поэтому все реальные D-триггеры имеют два входа: информационный D и синхронизации С (рис. 12). Под действием синхросигнала С информация, поступающая на вход D, принимается в триггер, но на выходе Q появляется с задержкой на один такт. В D-триггере с динамическим входом прием в триггер информации со входа D происходит в момент смены на входе С уровня 0 на уровень 1.

Рис. 12 – Схема D-триггера

Таблица 3

| C | D | Qt+1 |

|---|---|---|

| 1 | ||

| 1 | 1 | 1 |

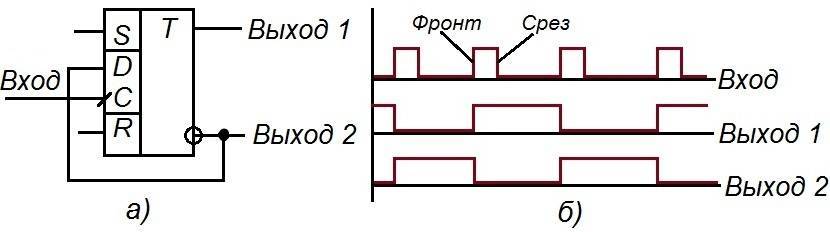

Условное графическое обозначение D-триггера показано на рис. 13.

Рис. 13 – Условное графическое обозначение D-триггера

Так как информация на выходе остается неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защелкой. Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке 14.

Рис. 14 – Временная диаграмма D-триггера

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера. Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы “защелкиваются” в этот момент. Отсюда и название – триггер-защелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера

Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту

Схема такого триггера приведена на рисунке 15, а обозначение на принципиальных схемах на рисунке 16.

Рис. 15 – Схема универсального D-триггера

Рис. 16 – Обозначение универсального D-триггера на принципиальных

схемах

На рис. 17 представлено условное обозначение D-триггера микросхемы К155ТМ2, содержащей два D-триггера. Входы R и S выполняют те же функции, что и в RS-триггере.

Рис. 17 – D-триггер микросхемы К155ТМ2

D-триггер несложно преобразовать в счетный триггер, т. е. такой, состояние которого изменяется после поступления очередного импульса на счетный вход. Для обеспечения счетного режима необходимо вход D соединить с инверсным выходом триггера (рис. 18,а). Из логики работы

D-триггера следует, что после прихода импульса на вход С состояние

триггера будет изменяться на противоположное. Это иллюстрируется

временными диаграммами, или эпюрами напряжений (рис. 18,б). Подобно

таблице истинности, эпюры напряжений дают наглядное представление о работе

устройства.

Рис. 18 – Работа D-триггера в счетном режимеа) – соединение выводов, б) – временные диаграммы

Необходимо отметить, что изменение состояния D-триггера данного типа происходит при изменении напряжения на счетном входе с низкого уровня на высокий. Такое изменение

напряжения часто называют положительным перепадом напряжения или фронтом импульса. Реакцию триггера на положительный перепад напряжения отображают

косой чертой, пересекающей линию входа С (рис. 18,а). Аналогично

изменение напряжения с высокого уровня на низкий называют отрицательным

перепадом напряжения, спадом или срезом импульса. На схемах это отображают

также косой чертой, но повернутой на 90° относительно показанной на

рисунке 18,а. В зависимости от своей внутренней структуры триггер реагирует или

на положительный, или на отрицательный перепад напряжения.

Триггеры. RS-триггеры. Асинхронный RS-триггер с инверсными входами

ТРИГГЕРЫ

Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит.

Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент.

Триггеры строятся на основе двух инвертирующих усилителей. Обобщенная схема представлена на рис.1.

Рис.1

Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время.

Триггер имеет два выхода: прямой Q

и инверсный. Состояние триггера определяют по значению сигнала на прямом выходеQ. Значения сигналов на прямом и инверсном выходах всегда противоположны.

Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ.

1.RS-триггеры ‘АсинхронныеRS-триггеры. В асинхронных триггерах срабатывание происходит непосредственно в момент изменения сигнала на информационных входах. АсинхронныеRS -триггеры являются наиболее простыми. В качестве самостоятельного устройства используются редко, но являются основой для построения более сложных систем.

RS

-триггер — это триггер с раздельной установкой состояний логического нуля и логической единицы. Он имеет два информационных входаS иR.. По входуS триггер устанавливается в состояниеQ =1( =0), по входуR— в состояниеQ =0(= 1). В зависимости от логической структуры асинхронныеRS -триггеры бывают с прямыми либо инверсными входами и могут строиться на двух логических элементах: 2ИЛИ-НЕ — триггер с прямыми входами; или на элементах 2И-НЕ — триггер с инверсными входами.

АсинхронныйRS-триггер с прямыми входами на логических элементах 2ИЛИ-НЕ представлен на рис. 2.

Рис.2.

Логические элементы ИЛИ-НЕ с инвертированием сигнала образуют петлю положительной обратной связи. При таком соединении логическая единица на выходе одного логического элемента (ЛЭ) поступает на вход другого ЛЭ и обеспечивает логический ноль (инвертирование) на его выходе. Логический ноль на выходе ЛЭ, поступая на вход другого, при инвертировании дает логическую 1. Таким образом, выходы Q

и всегда находятся в противоположных состояниях. Соединение элементов по данной схеме позволяет получить цепь с двумя устойчивыми состояниями.

Временные диаграммы, характеризующие работу асинхронного RS

-триггера с прямыми входами, показаны на рис. 3.

Рис.3

Для элементов ИЛИ-НЕ активным является высокий уровень — логическая 1, поэтому в режиме хранения данных на входы этого триггера подаются нулевые значения R

=S =0. Установка триггера в нужное состояние производится подачей на соответствующий вход активного уровня единицы. Одновременная подача единицы на оба входа (R и S) приводит к неопределенности. На обоих выходахQи появляются единицы, а после отключения входов (S=R=0) может установиться любое состояние

Триггер RS типа

Одной из простейших в цифровой электронике является схема RS-триггера на транзисторах. Внешним воздействием на вход прибора можно установить его выход в нужное устойчивое состояние. Схема устройства представляет собой каскады, выполненные на транзисторах. Вход каждого из них подключается к выходу противоположного. Два состояния определяются присутствием на выходе напряжения, а переход между ними происходит с помощью управляющих сигналов.

Вам это будет интересно Виды и применение греющего электрического кабеля

Работает схема следующим образом. Если в начальный момент времени VT2 будет закрыт, тогда через сопротивление R3 и коллектор будет течь ток, поддерживающий VT1 в режиме насыщения. Одновременно первый транзистор начнёт шунтировать базу VT2 и резистор R4. Режим отсечки VT2 соответствует значению логической единицы на выходе Q = 1, открытое состояние VT1 нулю, Q = 0. Амплитуда сигнала на коллекторе закрытого ключа определяется выражением: Uз = U * R3 / (R2+R3).

Для инверсии сигнала необходимо на вход R или S подать импульс. При этом если S = 1, то и Q = 1, а если R=1, то на выходе будет ноль. При значениях R1 = R2 и R3 = R4 триггер называется симметричным. Особенностью работы устройства является способность удерживать установленное состояние между импульсами R и S, что и используется для создания на нём элементов памяти.

На схемах RS-триггер обозначается в виде прямоугольника с подписанными входами S и R, а также возможными состояниями выхода. Прямой подписывается символом Q, а инверсный – Q. Информация может поступать на входы непрерывным потоком или только при появлении синхроимпульса. В первом случае устройство называют асинхронным, а во втором – синхронным (трактируемым).

Работа устройства наглядно описывается с помощью таблицы истинности.

Она наглядно показывает всевозможные комбинации, которые могут возникнуть на выходе прибора. Такая таблица составляется отдельно для триггера с прямыми входами и инверсными. В первом случае действующий сигнал равен единице, а во втором — нулю.