Транзисторные схемы

Транзисторные схемы работают достаточно похожим образом, и строятся на основе полевых транзисторов с изолированным затвором, так же известные как МОП-транзисторы (MOSFET), выполняющих роль переключателя. Однако, критерием “истинности” или “ложности” всей схемы является не протекающий ток, а значение напряжения (условно “высокое” или “низкое”)

Принципы работы полевых транзисторов

Полевые транзисторы состоят из двух полупроводниковых терминалов p- или n-типа (называемых исток (Source) и сток (Drain)), помещенных в субстрат соответственно n- или p-типа. N-тип соответствует электронной, а p-тип – дырочной проводимости. Сам транзистор обозначается по типу терминалов.

Так же присутствуют два терминала, называемых база (base) и затвор (gate), которые, собственно, и обеспечивают управление транзистором.

При приложении напряжения между базой и затвором, электроны или дырки притягиваются к области затвора, создавая канал проводимости между истоком и стоком. Изменение электрического поля между базой и затвором изменяет сопротивление этого канала.

Встречаются МОП-транзисторы с собственным (или встроенным) (depletion mode transistor) и индуцированным (или инверсным) каналом (enhancement mode transistor). Встроенный канал означает, что при нулевом напряжении затвор-база, канал транзистора открыт (т.е. проводит ток); для закрытия канала нужно приложить к затвору напряжение определенной полярности. Канал приборов с индуцированным каналом закрыт (не проводит ток) при нулевом напряжении затвор-база; для открытия канала нужно приложить к затвору напряжение определенной полярности. Полярность напряжения определяется типом проводников в транзисторе (N- или P-тип).

СИЗБNPPЗСИБ

Схема и условное обозначение PMOS с индуцированным каналом

СИЗБPNN

Схема и условное обозначение NMOS с индуцированным каналом

Схема и условное обозначение PMOS с собственным каналом

Схема и условное обозначение NMOS с собственным каналом

Часто терминал базы подключают напрямую к истоку.

Реализация логических операций на МОП-транзисторах

Независимо от типа транзистора, он может быть “настроен” таким образом, чтобы либо переходить в “открытое” состояние при подаче высокого напряжения (соответствующего логической единице) на затвор, либо низкого (соответствующего логическому нулю), и в “закрытое” в противном случае. При проектировании логических схем, имеет значение только этот фактор.

В этом контексте, транзисторы, переходящие в “открытое” состояние при подаче логической единицы на затвор, называются прямыми, а в “закрытое” – инверсными. При проектировании логики, часто используются следующие обозначения:

Прямой МОП-транзистор

Инверсный МОП-транзистор

Как правило, прямые транзисторы реализуются на NMOS, а инверсные – на PMOS.

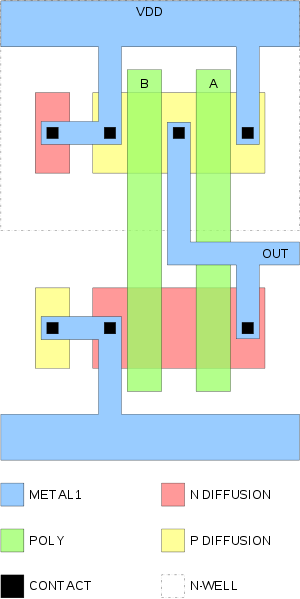

На основе этих двух типов строятся микросхемы типа CMOS (КМОП – комплементарная структура металл-оксид-полупроводник, она же COS-MOS), состоящие из симметрично расположенных p- и n-канальных полевых транзисторов. Использование симметричных схем позволяет значительно уменьшить ток активации схемы, и снизить энергопотребление.

Штрих Шеффера может быть реализован, например, так:

VccF = A | BAB

Штрих Шеффера на прямых транзисторах

VccAVccBF = A | B

CMOS-схема штриха Шеффера

Физическое устройство CMOS-схемы

Физическое устройство CMOS-схемы

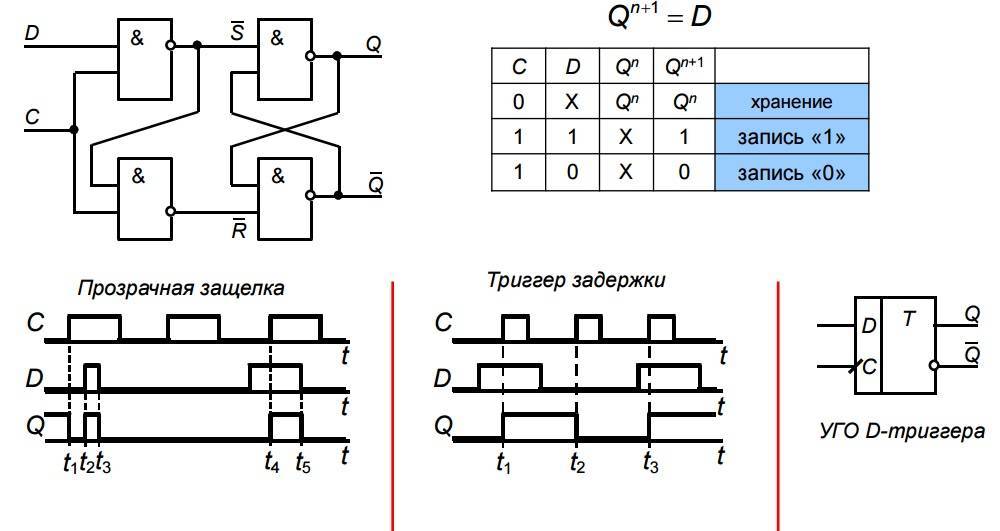

Логические схемы

На основе логических элементов строятся логические схемы. На логических схемах не рассматривается внутреннее устройство элементов, поэтому все логические схемы полностью эквивалентны логическим формулам, которые их выражают.

Для обозначения логических элементов, соответствующих базовым логическим операциям используются следующие обозначения:

&

Конъюнктор, соответствует операции конъюнкции.

1

Дизъюнктор, соответствует операции дизъюнкции.

Инвертор, соответствует операции инверсии.

И-НЕ (NAND), соответствует штриху Шеффера.

ИЛИ-НЕ (NOR), соответствует стрелке Пирса.

Физические реализации триггеров

Базовый элемент создают из полупроводниковых приборов, используя современные технологические процессы для миниатюризации функциональных изделий.

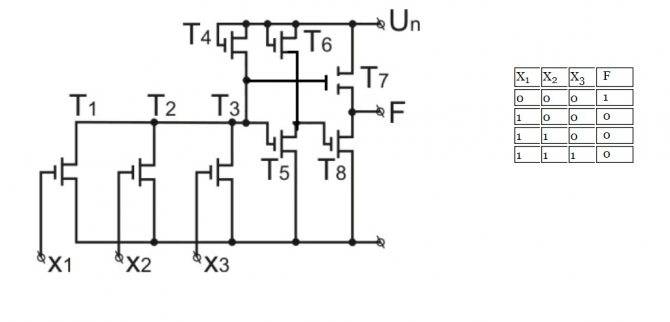

Логический элемент на МОП транзисторах

Триггеры с тиристорами

Для повышения мощности подключаемой нагрузки можно собрать триггер с применением тиристоров. К управляющему электроду присоединяют вход S, к затвору – R. Для поддержания постоянного напряжения на аноде подойдет транзистор, включенный в соответствующую цепь.

Триггеры на релейно-контакторной базе

Несмотря на общие тенденции миниатюризации, вполне допустимо создать функциональный триггер из реле. Подобные решения, в частности, применяют для защиты цепей питания при включении мощных электроприводов.

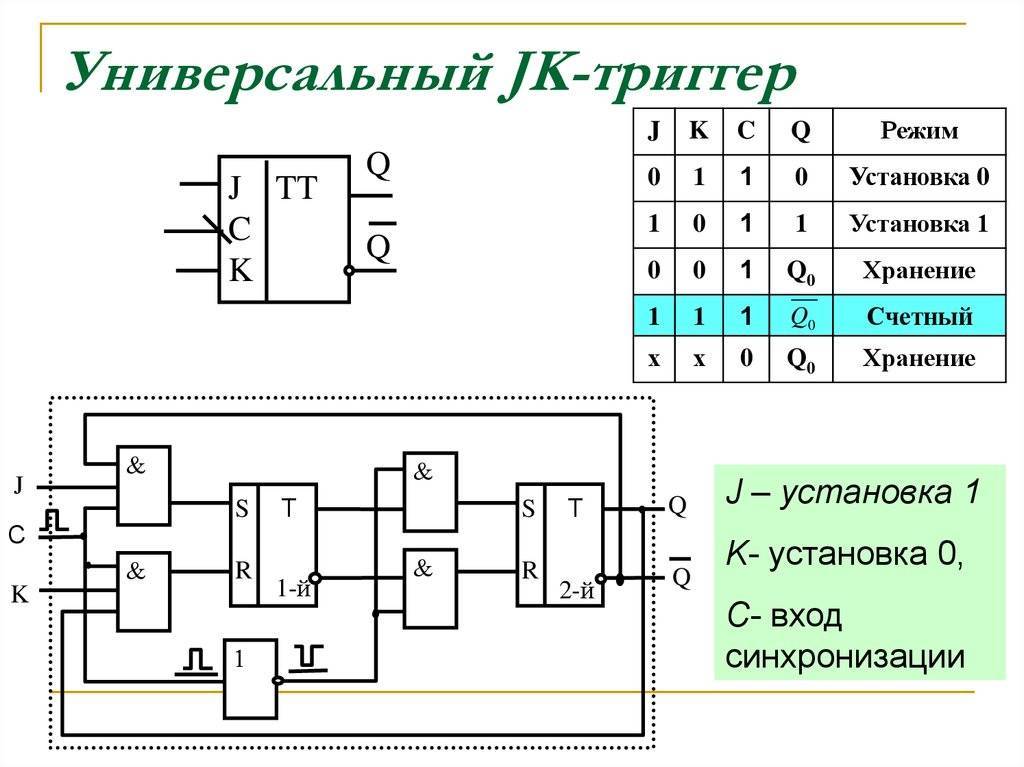

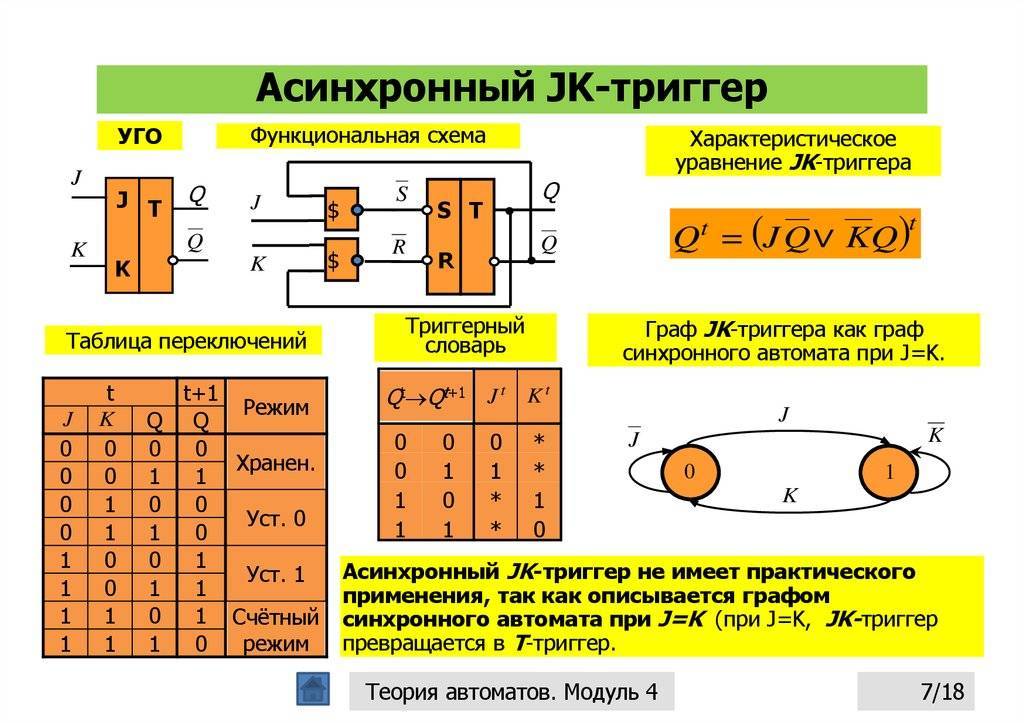

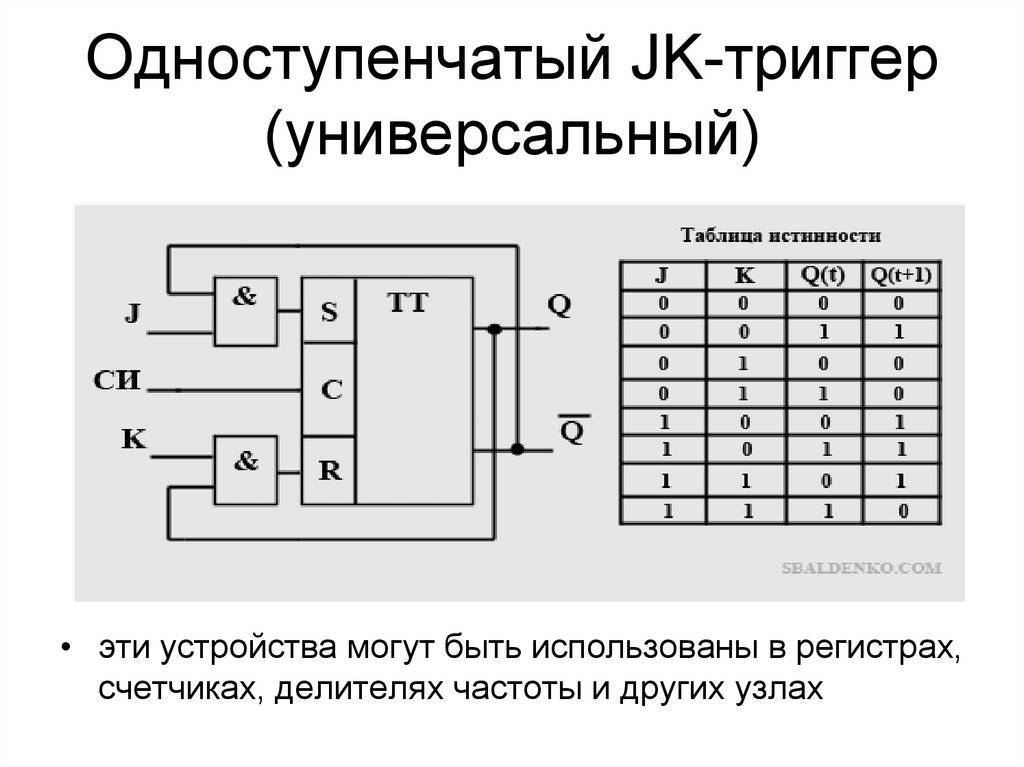

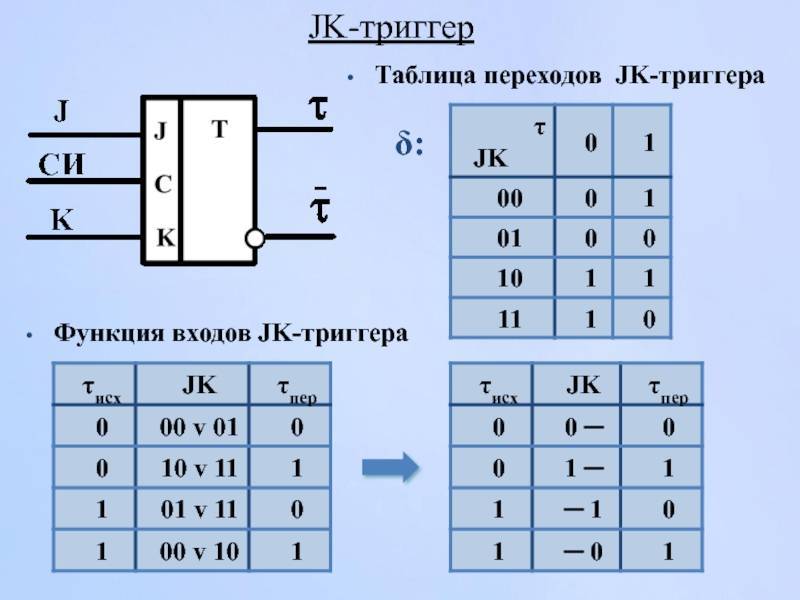

Назначение, схема и принцип работы JK-триггер

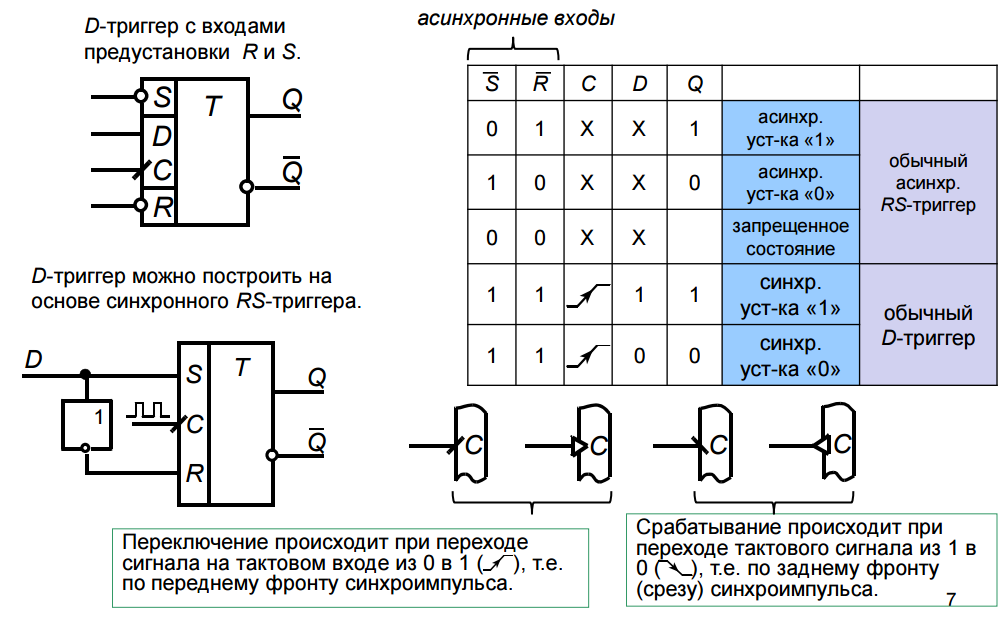

JK-триггер с дополнительными асинхронными инверсными входами S и R

| J | K | Q(t) | Q(t+1) |

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump

— прыжок) аналогичен входуS у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входуR у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и Kучитываются только в момент тактирования, например по положительному фронтуимпульса на входе синхронизации. На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и Kлогической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К.

Алгоритм функционирования JK-триггера можно представить формулой

Условное графическое обозначение JK-триггера со статическим входом С

Назначение, схема и принцип работы счетчиков импульсов.

Электронный счетчик импульсов предназначен для подсчета количества импульсов, поступающих с измерительных датчиков на счетные входы (или один счетный вход) счетчика импульсов и пересчета их в требуемые физические единицы измерения путем умножения на заданный множитель (например, в метры, литры, штуки, килограммы и т. д.); подсчета суммарной выработки за смену, сутки, неделю, месяц и т. д.; управления исполнительными механизмами одним или несколькими дискретными выходами (чаще всего, в счетчиках импульсов в качестве дискретного выхода используется реле или оптопара).

Как правило, в качестве датчика применяется механический прерыватель илииндуктивный датчик (бесконтактный датчик) или энкодер.

Электронные счетчики импульсов могут иметь высокую степень защиты IP (степень защиты оболочки) от пыли и воды (например, IP65).

Счетчик импульсов (некоторые модели) может иметь встроенную функцию тахометра илирасходомера.

Электронные счетчики импульсов сохраняют результат измерений при исчезновении напряжения питания в течение неограниченного периода времени в энергонезависимой памяти (EEPROM). После возврата напряжения питания счет импульсов продолжается, начиная с сохраненного значения; некоторые модели счетчиков импульсов индицируют факт пропадания напряжения питания во время работы.

Некоторые модели имеют интерфейс для подключения к сети или компьютеру (например, RS485, RS232, CAN), а также аналоговый выход ЦАП, который может быть использован как для передачи информации другим контрольно-измерительным приборам управления исполнительными механизмами (например, электроприводом).

Кроме того, счётчики импульсов классифицируют по направлению счета (режиму работы):

суммирующие счетчики импульсов;

вычитающие счетчики импульсов;

реверсивные счетчики импульсов.

Импульсы от энкодера с определением направления вращения

Реверсивные счетчики импульсов чаще всего используются при работе с 2-х канальнымиэнкодерами или с двумя индуктивными датчиками, при этом:

автоматически счетчиком импульсов определяется направление вращения энкодера;

происходит увеличение в 4 раза разрешающей способности энкодера, то есть 1 полный импульс c энкодера счетчик импульсов превращает в 4 инкремента (см. рис. поясняющий работу счетчика импульсов в реверсивном режиме).

Мультиплексор

- Мультиплексор

- логический элемент, имеющий несколько сигнальных входов, один (или более) управляющих входов и один выход

- позволяет передавать сигнал с одного из входов на один выход

Простейший вариант – однобитный мультиплексор с двумя сигнальными входами – использует однобитный управляющий вход. В общем случае, число бит управляющего входа должно быть не менее \(\ceil {\log_2 N},\) где \(N\) – число сигнальных входов, \(\ceil \cdot\) – округление вверх, т.к. именно столько бит необходимо для выбора одного из сигнальных входов (следует из числа возможных комбинаций \(x\) бит равного \(2^x\))

| S | A | B | Z |

|---|---|---|---|

| 1 | |||

| 1 | 1 | ||

| 1 | 1 | 1 | |

| 1 | |||

| 1 | 1 | 1 | |

| 1 | 1 | ||

| 1 | 1 | 1 | 1 |

По таблице истинности легко можно составить формулу:

\

Или, на основе штриха Шеффера:

\

ABZS

Реализация на элементах И-НЕ

Мультиплексор считается базовым компонентом логических схем, часто изображается одним блоком и помечается символами “MS” (от “multiple select”) или “MUX” (от “multiplexor”)

MSABS

Изображение на схемах

Варианты реализации триггера

Прецизионный триггер Шмитта

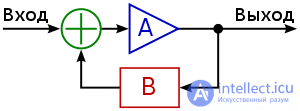

Триггер Шмитта представляет собой RS-триггер, управляемый одним входным аналоговым сигналом, с двумя разными напряжениями переключения в два различных состояния. Прецизионным его называют потому, что пороги переключения задаются независимо и точность этих порогов зависит только от точности порогов переключения входных одновходовых компараторов. Обычно состояния выходного сигнала триггера обозначаются символами «0» и «1», причем, напряжение переключения в «1» выше напряжения переключения в «0». При входном напряжении находящемся между напряжениями переключения триггер Шмитта находится в состоянии хранения ранее записанной в него информации и его выходной сигнал определяется предысторией изменения входного сигнала.

Триггеры Шмитта с RS-триггером не имеют обратной связи с выхода на аналоговый вход. Они состоят из двухпорогового компаратора, в котором сравниваются два раздельно устанавливаемых напряжения порогов переключения с входным сигналом. Переключение триггера в состояние «0» и в состояние «1» происходит от выходных сигналов однопороговых компараторов, которые подаются на асинхронные входы установки и сброса S и R RS-триггера.

Триггер Шмитта с обратной связью

Триггер Шмитта на компараторе с положительной обратной связью. — однопороговый компаратор с ограниченными на уровне выходными напряжениями в двух разных состояниях; — делитель напряжения в петле положительной обратной связи.

В вариантах триггера с обратной связью, обратная связь используется и для переключения напряжения порога сравнения в обычном компараторе, который имеет порог переключения равным нулю, превращая его одновременно в двухпороговый компаратор с разными порогами и в RS-триггер на одном и том же однопороговом компараторе. При высоком напряжении (состояние логической «1») на выходе компаратора, обратная связь снижает напряжение порога переключения по входу Input, так как суммируется входным сумматором с входным сигналом, для того, чтобы напряжение на входе компаратора, равное выходному напряжению сумматора, стало равным нулю, входное напряжение должно стать отрицательным и равным по модулю выходному напряжению компаратора, находящегося в состоянии логической «1». Соответственно, при низком напряжении на выходе компаратора (состояние логического «0») на выходе компаратора обратная связь увеличивает напряжение порога переключения.

В такой структуре затруднены раздельная и независимая установка порогов срабатывания. Кроме того, при входном напряжении, значение которого лежит между порогами переключения, то есть в зоне неоднозначности, принудительная установка триггера в заданное состояние требует применения дополнительных компонентов.

Алгоритм работы

Если на вход C поступает сигнал, равный нулю, то выходные значения будут сохранены. Как только он станет равным единице, формирование значения Q будет происходить по следующим правилам:

- Если J=K=0, режим триггера не меняется.

- Когда J и K равны 1, происходит изменение состояния элемента на противоположное при поступлении каждого тактового импульса. В этом случае триггер функционирует идентично делителю частоты. Такой режим работы называют счётным, поскольку его использование позволяет осуществлять подсчёт определённых событий.

- При K = 1, J = 0 выходное значение принимает нулевое значение.

- Если K = 0, J = 1, тогда на выходе будет получена единица.

Алгоритм работы отображает таблица истинности JK-триггера, так как каждой входной комбинации значений соответствует строго определённая выходная.

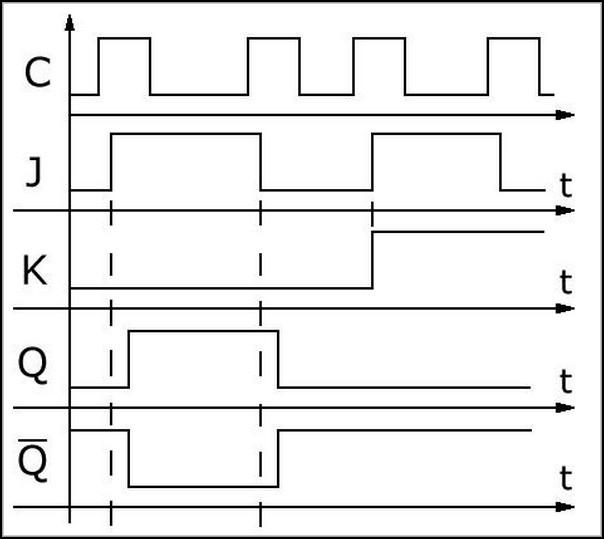

Разобраться в работе триггера помогает еще временная диаграмма, на которой графически отображаются сигнальные импульсы, присутствующие одновременно на входах и выходах устройства.

На приведённой диаграмме срабатывание происходит по фронту импульса C с задержкой. Момент, когда это происходит, зависит от конкретной схемы реализации.

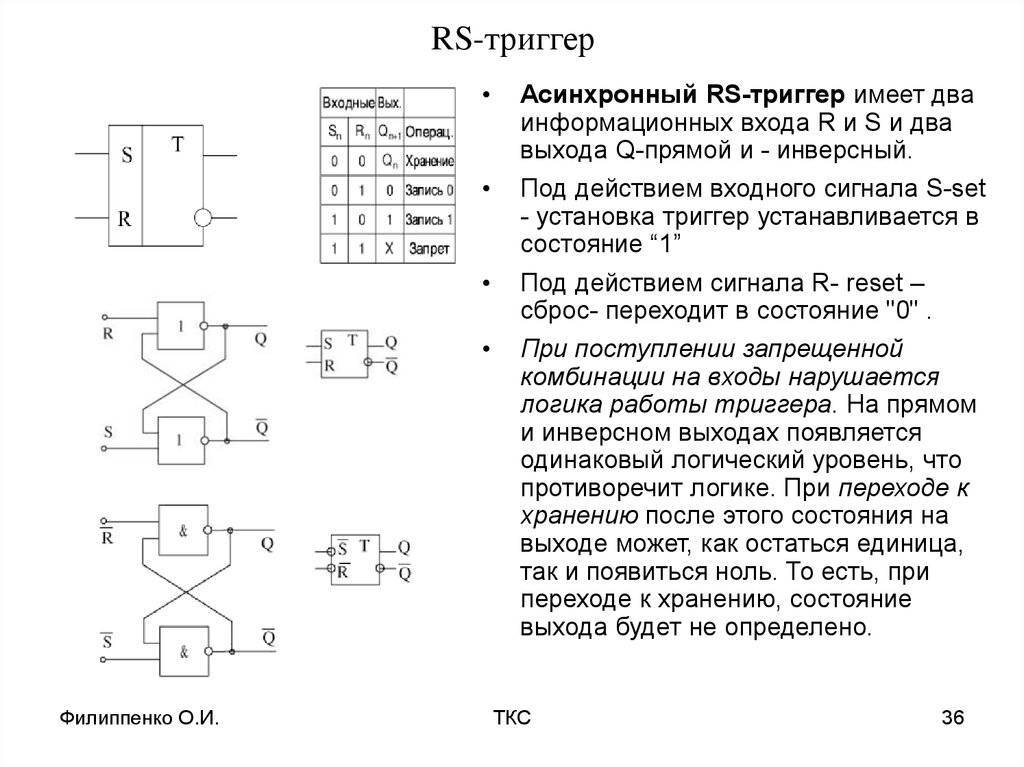

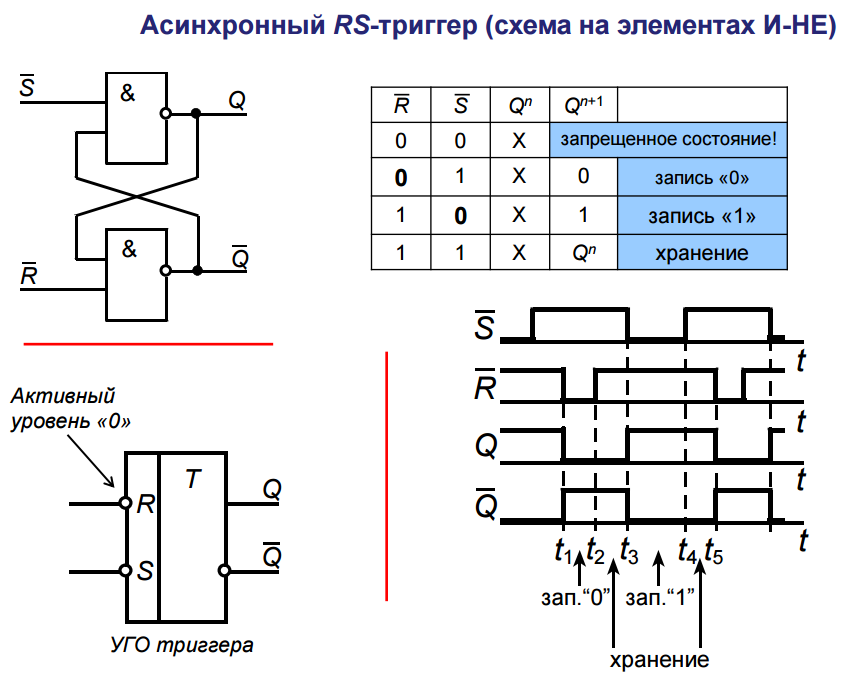

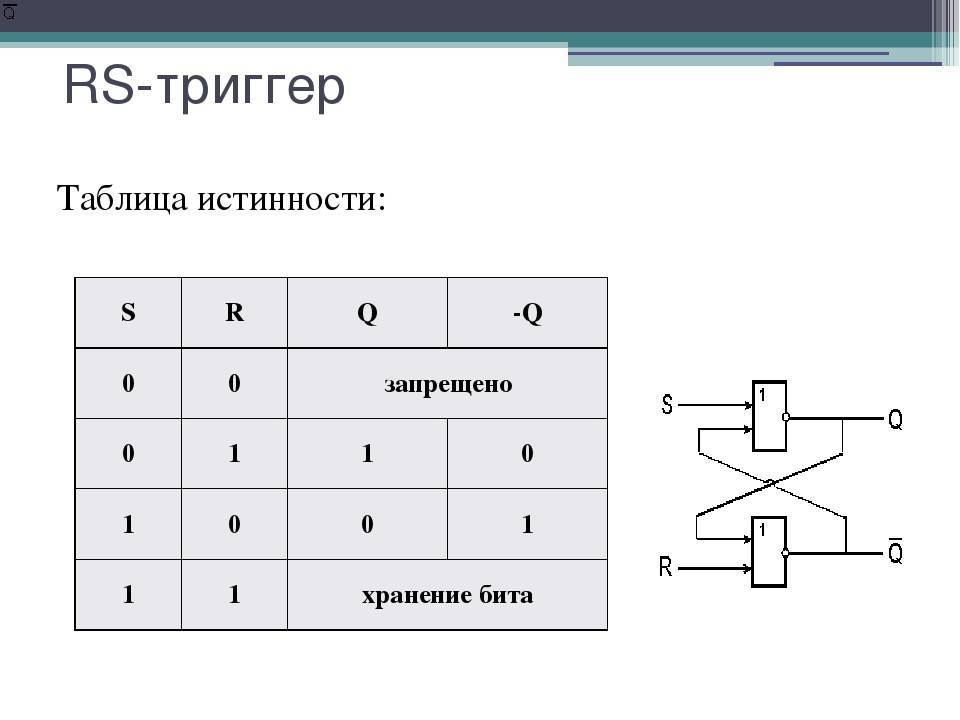

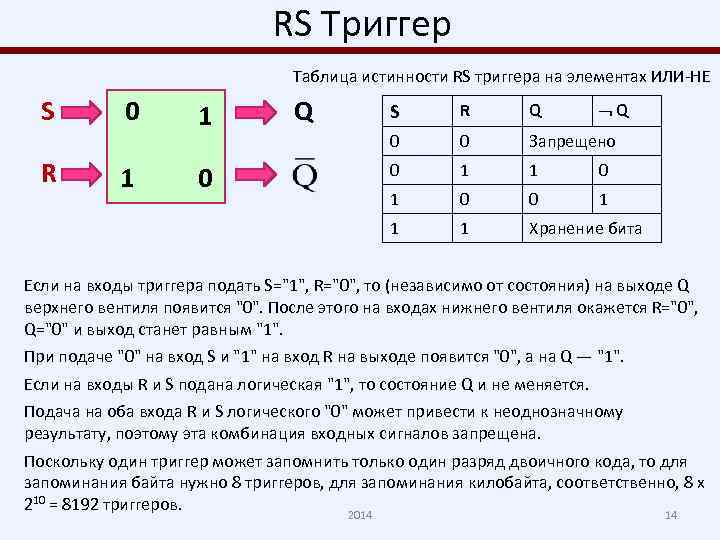

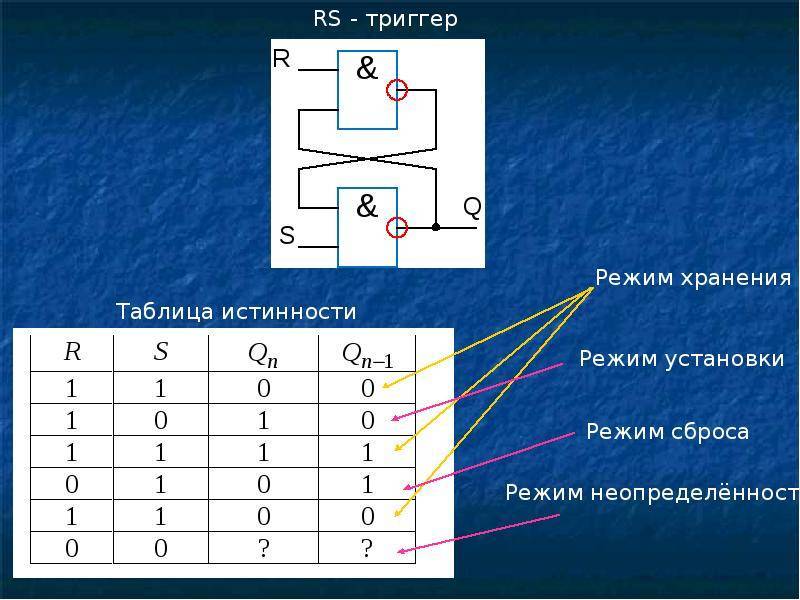

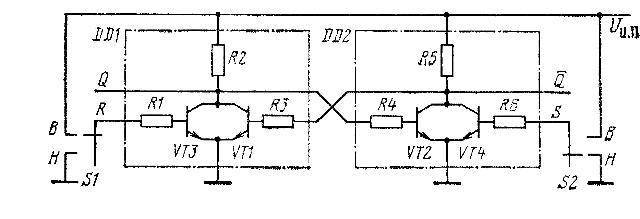

Принцип работы RS триггера

Система, представленная выше, при помощи электромагнитных реле иллюстрирует работу триггера на элементах ИЛИ-НЕ. Однако в современных схемах электромеханические приборы давным-давно не используются, сейчас они собираются из электронных логических элементов на транзисторах, заключенных внутри интегральных микросхем. К тому же для их реализации можно использовать различные базисы. Пример схемы RS триггера на элементах И-НЕ, охваченных положительной обратной связью.

Допустим, что на оба входа R и S подаются единицы. Если верхний элемент И-НЕ выдаст на прямой выход Q логический 0, благодаря положительной обратной связи он поступит на свободный вход нижнего элемента, вследствие чего тот выдаст на инверсном выходе единицу (1). В свою очередь, эта 1 по обратной связи поступает на вход верхнего элемента, тем самым подтверждая 0 на выходе Q. Если же на прямом выходе изначально находится 1, то инверсный, соответственно, выдаст 0, который подтвердит 1 на выходе Q.

Транзисторная схема RS триггера

При подаче на S-вход 0, согласно логической функции И-НЕ, на прямом выходе Q возникнет 1, а на инверсном – 0. Если при этом на вход S снова подать 1, состояние триггера не изменится, так как по таблице истинности И-НЕ при подаче на входы элемента комбинации 0 и 1 либо 0 и 0, на выходе всегда будет 1. Таким образом, триггерная схема сохраняет полученное значение неизменным. Сбросить значение Q обратно в 0 можно, только подав сигнал на сбрасывающий вход R. Практически работу RS триггера можно пронаблюдать, собрав такую схему на транзисторах.

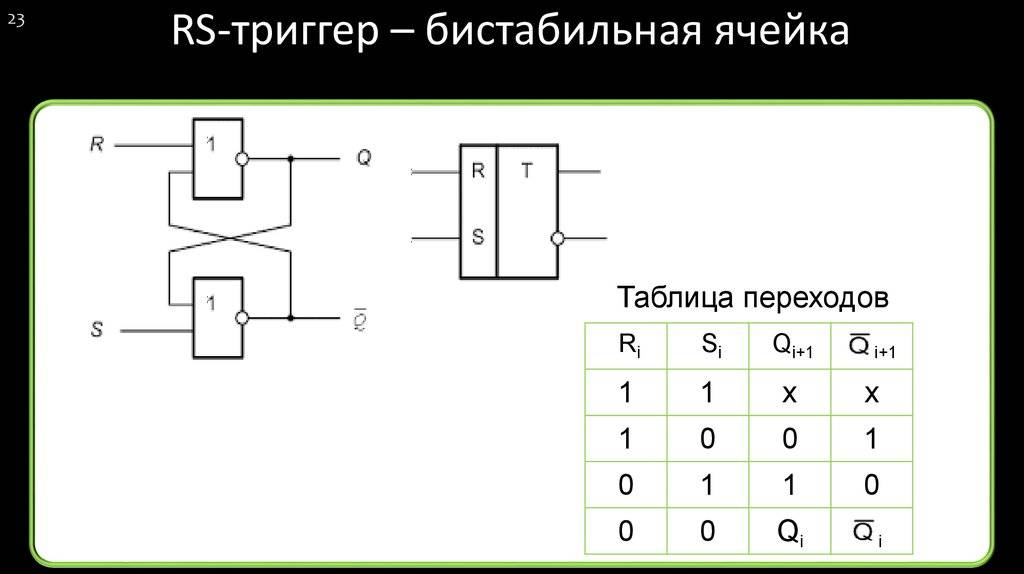

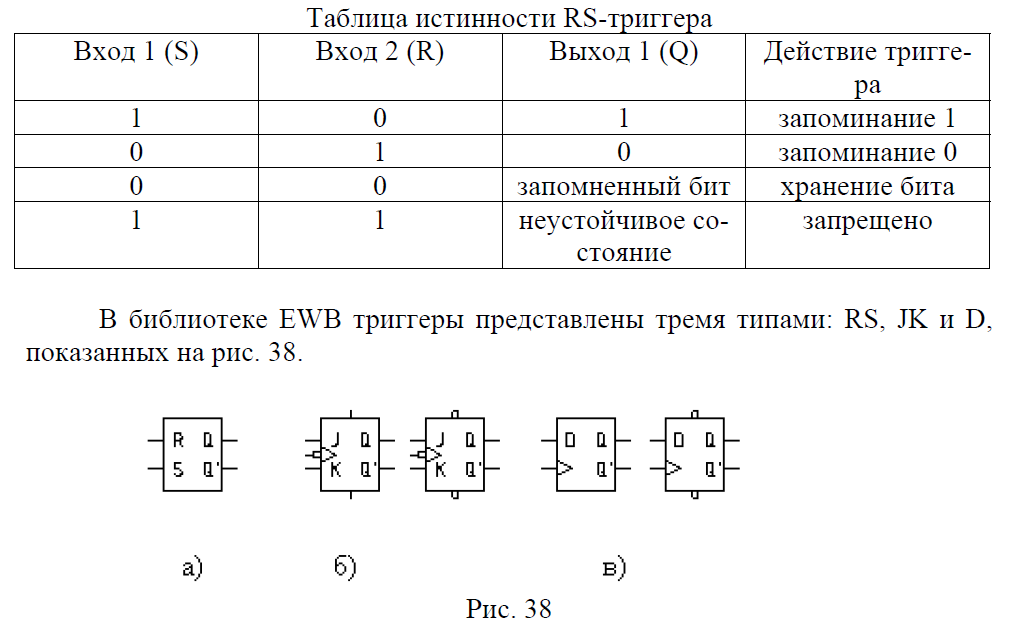

RS-триггеры

Логические устройства вычислительной техники

Что же такое RS-триггеры? В моем понимании — это устройства, которые могут принимать одно из двух состояний. На основании этого можно сделать вывод, что этот логический элемент может хранить один бит информации (грубо говоря, ноль или единицу). Существуют некоторые типы данного вида RS-триггеров. Давайте рассмотрим один из них:

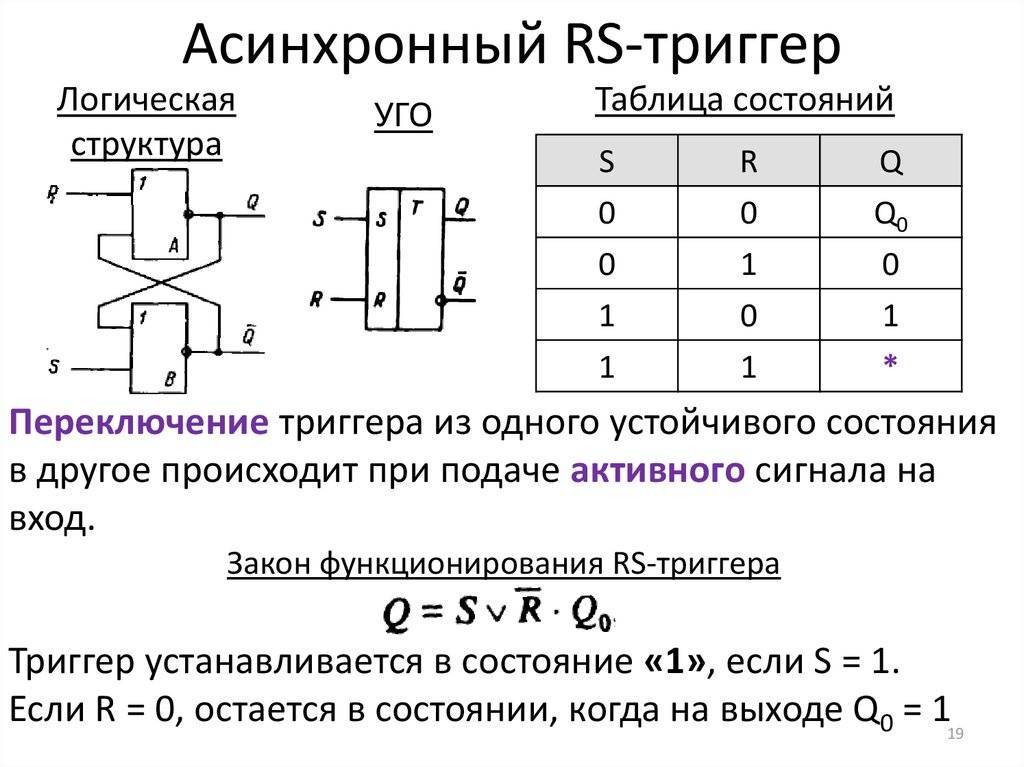

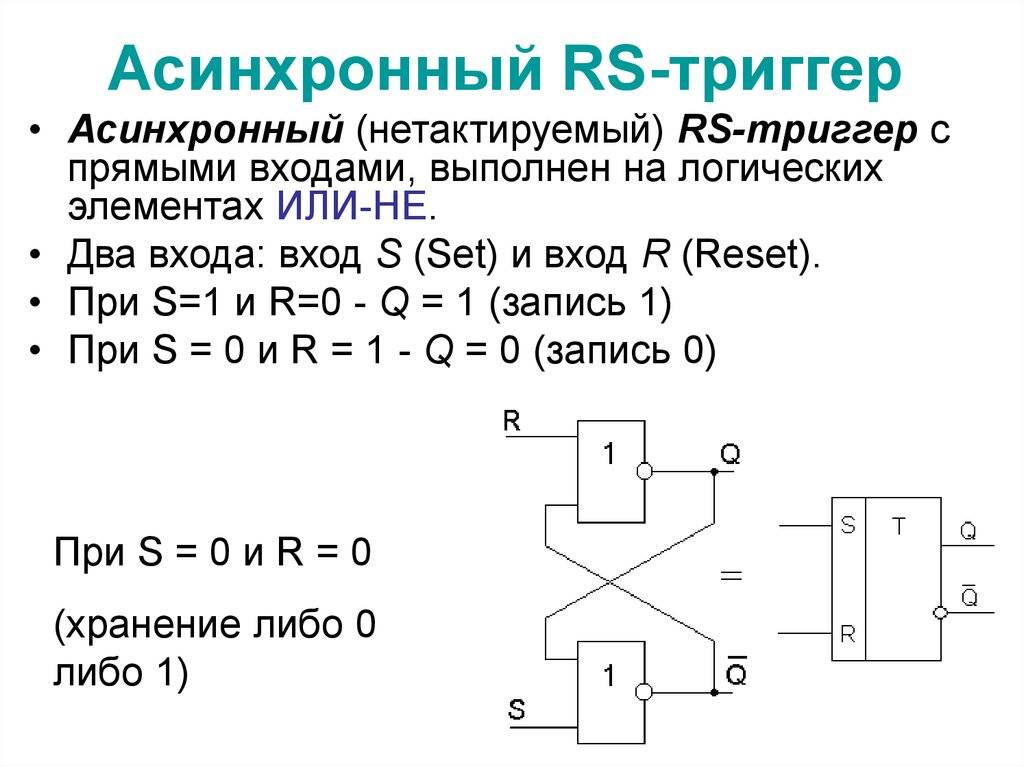

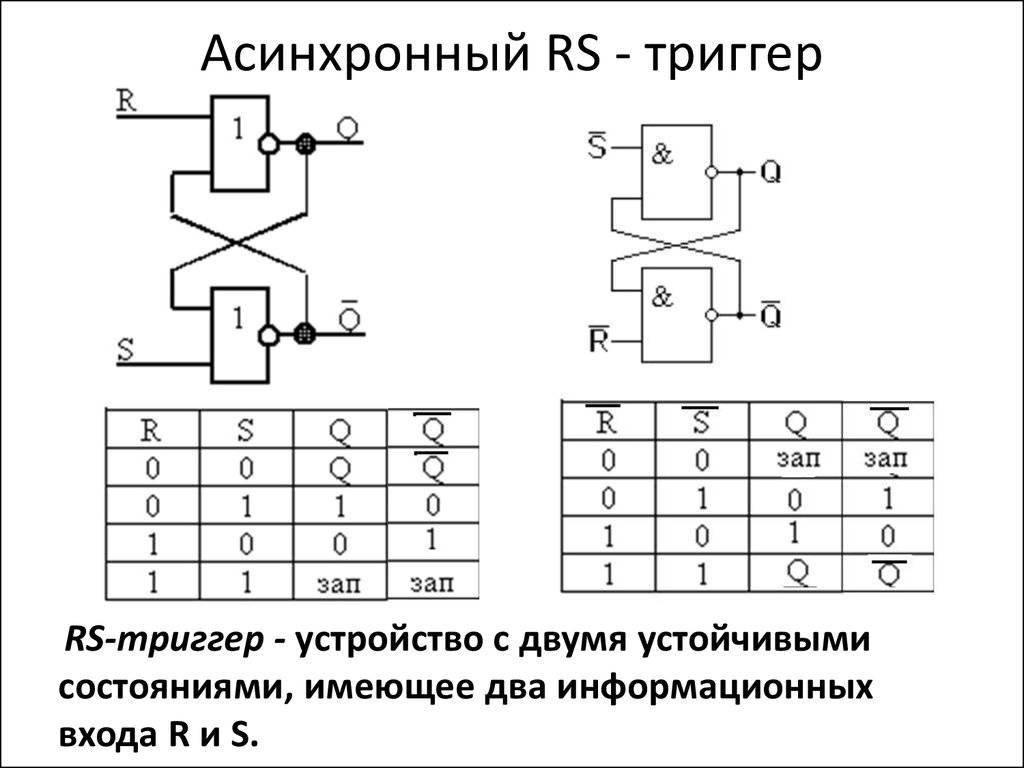

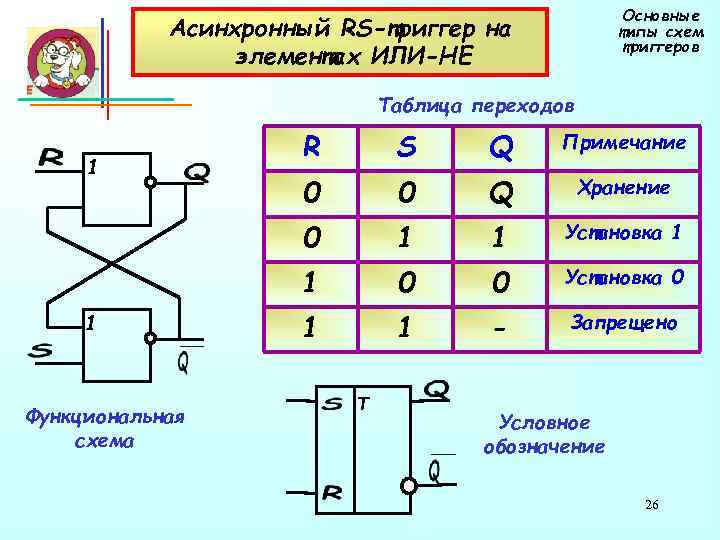

Асинхронный RS-триггер

Имеет два входа “R» и «S” и два выхода, как правило это “Q” и “не Q” (т.е. инверсный) . Лично я запомнил, какой элемент для чего, после того, когда узнал, что R – это “RESET” (что означает “сброс”) и “S” – это “SET” (что означает установка)

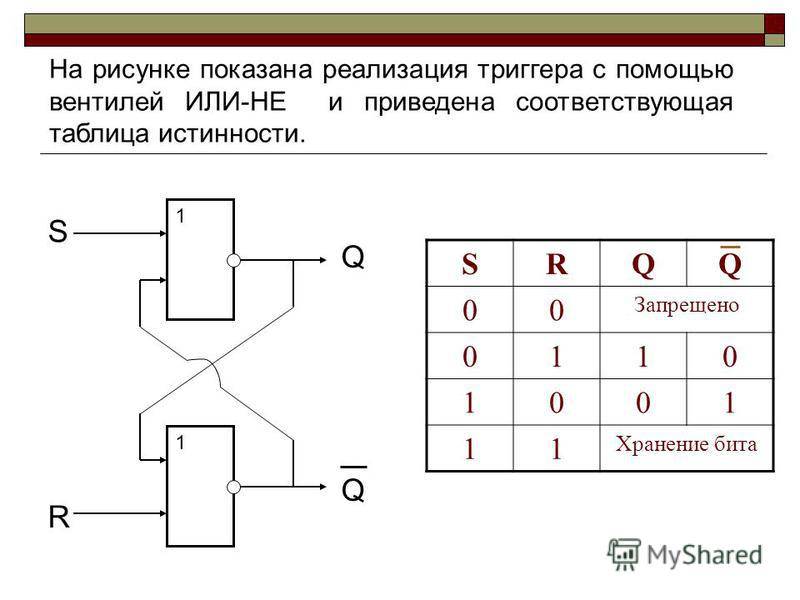

Принимая во внимание изложенную информацию можно указать, что при подаче сигнала (единица) на “S” на выходе “Q” устанавливается единица, а при подаче единицы на “R” приводит к сбросу единицы на выходе “Q” и установки на нем нуля. Рассмотрим работу на базе элементов “2ИЛИ-НЕ” и “2И-НЕ”

Для этого используем графическое изображение этих элементов.

Итак, разберем принцип работы RS-триггера на базе элементов “2ИЛИ-НЕ”. В начальном положении, когда на R и S отсутствуют сигналы (логический “0”), на выходе “Q” присутствует также “0” или “1” – это исходное состояние. Выглядит это так:

Далее подадим на “S” логическуюединицу и получим на выходе “Q” также единицу. Будет выглядеть это так.

Следующим шагом подадим логическую единицу на “R” и уже на “Q” получим “0”. Изобразим это на рисунке.

Более наглядную работу RS-триггера на элементах 2ИЛИ-НЕ можно продемонстрировать, изобразив таблицу истинности. Вот так она выглядит.

Сейчас рассмотрим работу на элементах 2И-НЕ. Выглядит она аналогично, как и на элементах 2ИЛИ-НЕ с той лишь разницей, что активным уровнем является не “1”как в предыдущем случае, а “0”. Убедимся в этом, используя рисунок и таблицу истинности.

Асинхронным триггерам свойственно такое явление как присутствие “гонок”, что это? Это не одновременное или даже не согласованное по времени поступление информации на входы. Это приводит к наложению одного сигнала на другой. Чем это вызвано? А вызвано это разным временем быстродействия элементов, через которые проходит сигнал, прежде чем попасть на входы триггера, в данном случае на “R” или “S”. Покажем это явление на диаграмме.

Чтобы избавиться от этого явления, был придуман вариант подачи синхросигнала и асинхронный триггер превратился в синхронный.

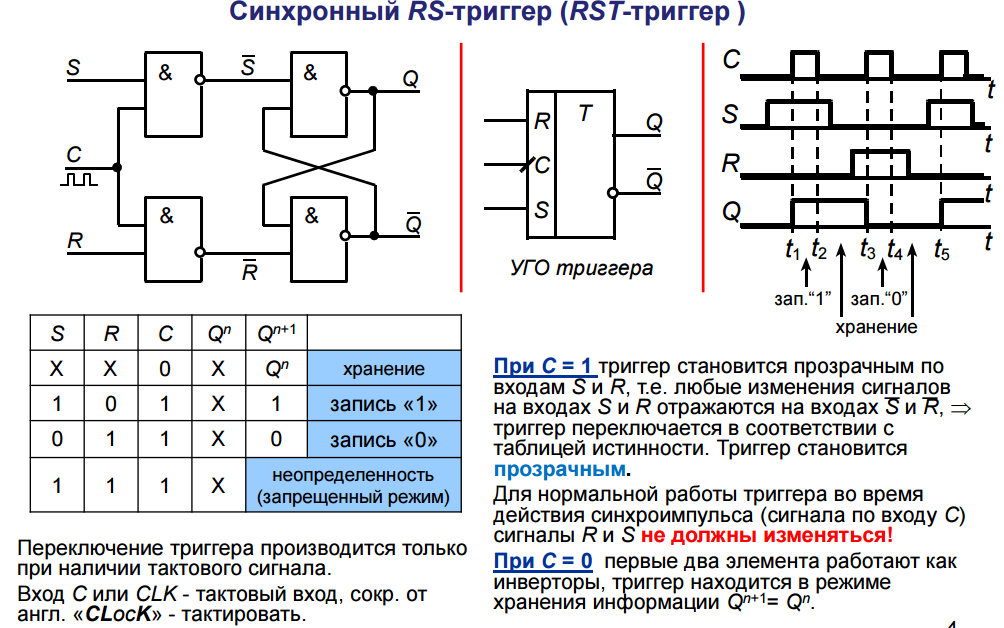

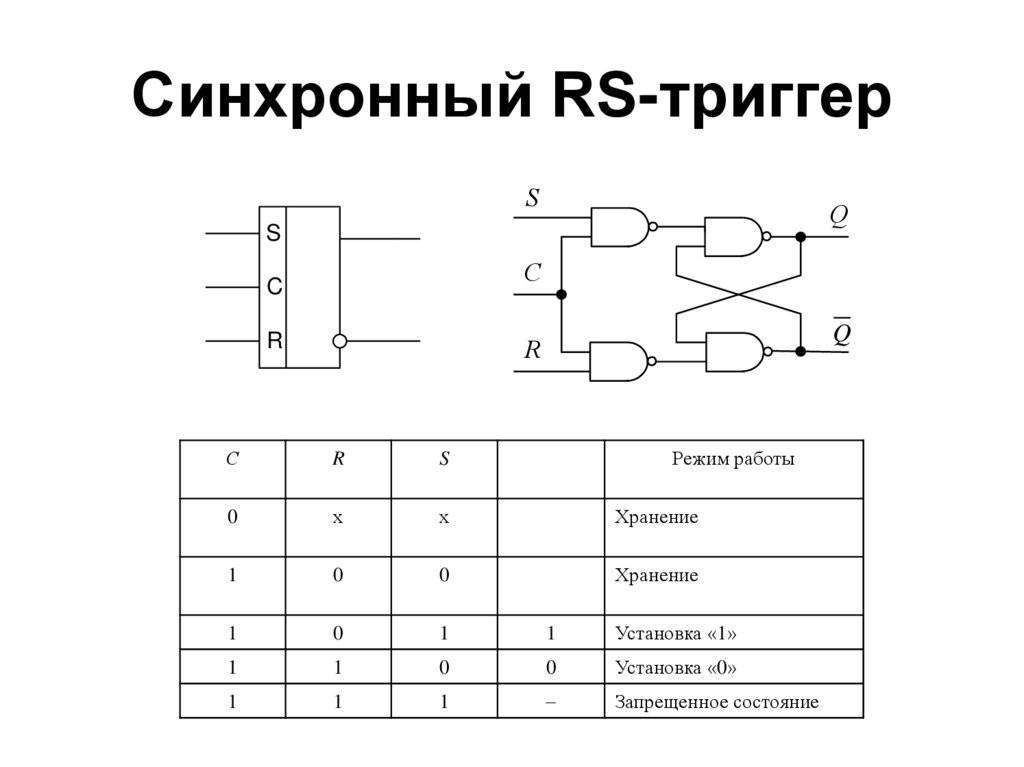

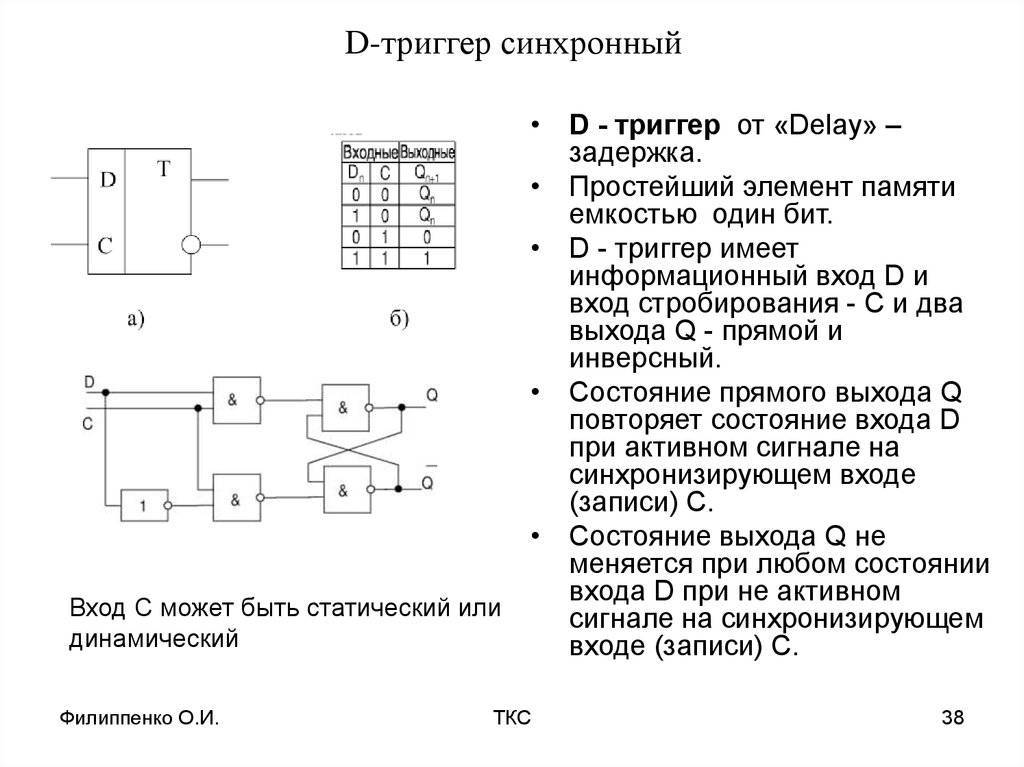

Синхронные RS–триггеры

Этот вид логического устройства отличается от рассмотренного выше тем, что у него помимо входов “R” и “S” присутствует и третий “C”, на который подаются синхроимпульсы. Без этих импульсов информация на “R” и ”S” восприниматься не будет. Схему синхронного RS–триггера и диаграмму работы изобразим графически.

Из диаграммы видно, что в данном случае срабатывание происходит по переднему фронту (но бывает и по спаду) синхроимпульса.

Передний фронт синхроимпульса – это участок прямоугольного импульса, где происходит его возрастание.

Спад синхроимпульса – это участок спада синхроимпульса.

Именно здесь сделаем небольшое отступление и укажем, что бывают триггеры динамические и статические и соответственно со статическим и динамическим управлением. Чем они отличаются? Объясним максимально просто.

Динамические триггеры – на выходах, которых присутствуют либо непрерывная последовательность импульсов определенной частоты, либо ее отсутствие. (Напоминает управляемый генератор).

Статические триггеры– на выходах которых присутствуют неизменный уровень напряжения, либо его отсутствие.

Со статическим управлением – восприятие сигналов на информационных входах происходит только при подаче на “С” логической единицы (логического нуля).

С динамическим управлением – восприятие сигналов на информационных входах происходят в моменты перепада сигнала на “С”(Передний фронт синхроимпульса или спад синхроимпульса).

Если логические функции входов зависят от его выходов, то целесообразно использовать более рациональную конструкцию элементов.

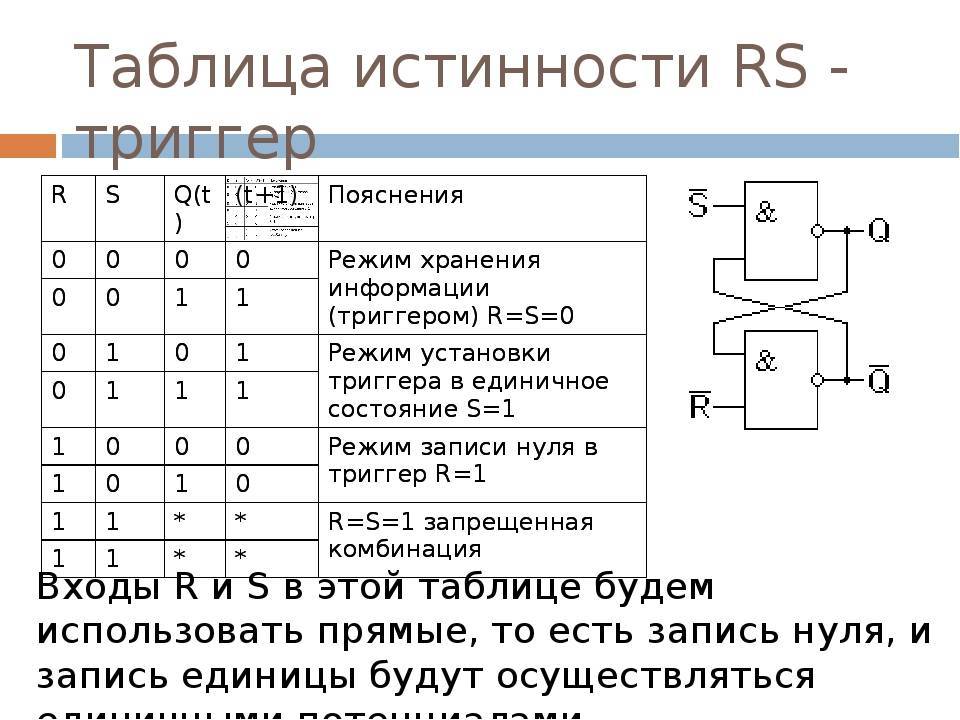

RS — триггер

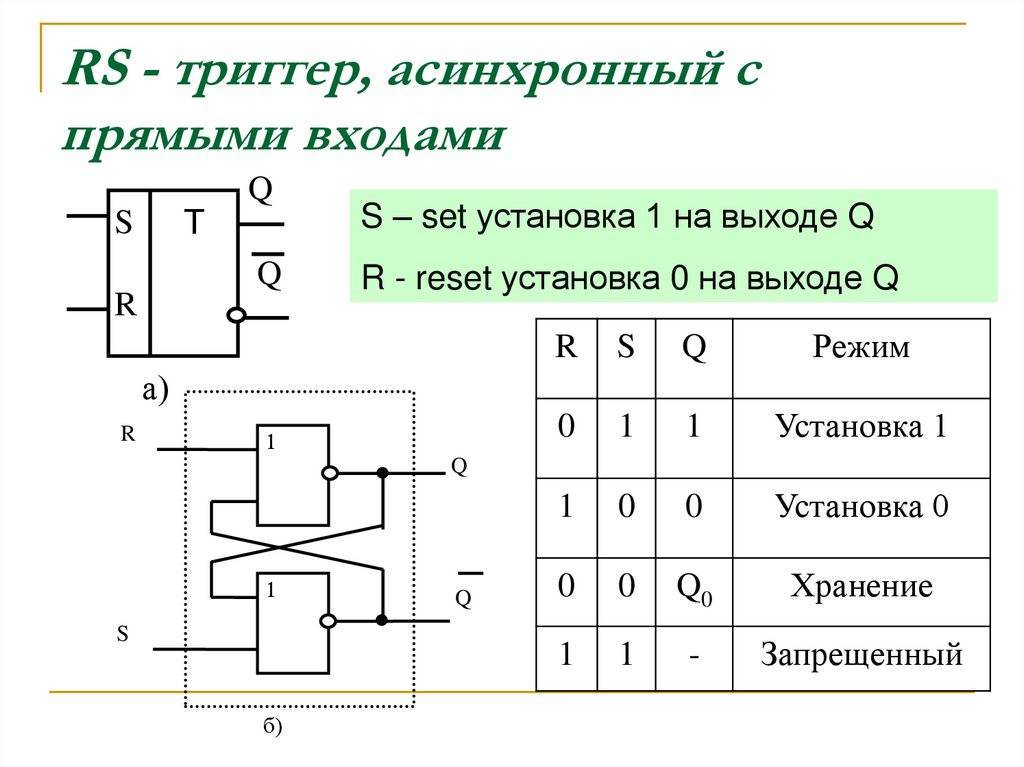

Первым будет рассмотрен RS-триггер. Его условное обозначение приведено на рисунке 1.

S (SET) — вход установки значения 1. R (RESET) — вход сброса (установки значения 0). Входы прямые — активны при подачи логической единицы, неактивны при подаче логического нуля.

Логика работы RS-триггера:

- S=0 R=0 — режим хранения информации (выходы не меняются, Q(t+1)=Q(t) )

- S=1 R=1 — режим записи единицы ( Q(t+1)=1 )

- S=0 R=1 — режим записи нуля ( Q(t+1)=0 )

- S=1 R=1 — запрещенная комбинация (оба входа активны). Значение Q зависит от реализации триггера (не определено в общем случае). Значение перехода из запрещенного состояния Q(t) в Q(t+1) тоже зависит от реализации.

RS — триггер с инверсными входами (рис. 2) работает аналогично, только входы становятся активны при подаче логического нуля, а неактивны при подаче единицы.

Классическая реализация RS-триггера

Классической является реализация RS-триггера на элементах «ИЛИ-НЕ» (рис 3.):

| S | R | Q(t) | Q(t+1) | no Q(t+1) | Описание |

| 1 | режим хранения нуля | ||||

| 1 | 1 | режим хранения единицы | |||

| 1 | 1 | установка в состояние 1 | |||

| 1 | 1 | 1 | режим хранения 1 | ||

| 1 | 1 | режим хранения нуля | |||

| 1 | 1 | 1 | сброс в ноль | ||

| 1 | 1 | запрещено | |||

| 1 | 1 | 1 | запрещено |

Временные диаграммы RS-триггера

Будем считать, что в триггере записано значение «0», попробуем записать «1» (рис. 4).

Если объединить входы R и S триггера, то выход будет определяться тем, какой из элементов сработает раньше («генератор случайных чисел»). Схема и временные диаграммы такого подключения приведены на рисунке 5.

Таблица истинности jk триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, его схема изменена таким образом, что при подаче двух единиц jk триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов он изменяет своё состояние на противоположное. Таблица истинности jk триггера приведена в таблице 1.

Таблица 1. Таблица истинности jk триггера.

| С | K | J | Q(t) | Q(t+1) | Пояснения |

| x | x | Режим хранения информации | |||

| x | x | 1 | 1 | ||

| 1 | Режим хранения информации | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы J=1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим записи нуля K=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | 1 | K=J=1 счетный режим триггера | |

| 1 | 1 | 1 | 1 |

Один из вариантов внутренней схемы JK-триггера приведен на рисунке 1. Он построен по классической двухтактной схеме. Приведенная на рисунке 1 схема удобна для изучения принципов работы данного триггера в счетном режиме.

Рисунок 1. Внутренняя схема jk триггера

Для реализации счетного режима в схеме введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация, а то, что она перекрестная, вводит новый режим работы — счетный. При подаче на входы j и k логической единицы одновременно JK-триггер переходит в счетный режим, подобно T триггеру.

Приводить временные диаграммы работы JK-триггера не имеет смысла, так как они совпадают с приведёнными ранее временными диаграммами RS- и . Условно-графическое обозначение приведено на рисунке 2.

Рисунок 2. Условно-графическое обозначение jk триггера

Цифровые микросхемы обычно собираются на элементах «И-НЕ». Тогда схема, приведенная на рисунке 1, преобразуется в схему, показанную на рисунке 3.

Рисунок 3. jk триггер, собранный на логических элементах «И-НЕ»

В промышленно выпускающихся микросхемах обычно кроме входов j и k реализуются входы R и S, которые позволяют устанавливать jk-триггер в заранее определённое исходное состояние. Именно так реализованы микросхемы 155ТВ1, 133ТВ1, SN7472. На рисунке 4 приведена цоколевка этих микросхем.

Назначение, схема и принцип работы JK-триггер

Главная Избранные Случайная статья Познавательные Новые добавления Обратная связь FAQ

⇐ ПредыдущаяСтр 6 из 9Следующая ⇒

JK-триггер с дополнительными асинхронными инверсными входами S и R

| J | K | Q(t) | Q(t+1) |

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump

— прыжок) аналогичен входуS у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входуR у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и Kучитываются только в момент тактирования, например по положительному фронтуимпульса на входе синхронизации. На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и Kлогической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К.

Алгоритм функционирования JK-триггера можно представить формулой

Условное графическое обозначение JK-триггера со статическим входом С

Назначение, схема и принцип работы счетчиков импульсов.

Электронный счетчик импульсов предназначен для подсчета количества импульсов, поступающих с измерительных датчиков на счетные входы (или один счетный вход) счетчика импульсов и пересчета их в требуемые физические единицы измерения путем умножения на заданный множитель (например, в метры, литры, штуки, килограммы и т. д.); подсчета суммарной выработки за смену, сутки, неделю, месяц и т. д.; управления исполнительными механизмами одним или несколькими дискретными выходами (чаще всего, в счетчиках импульсов в качестве дискретного выхода используется реле или оптопара).

Как правило, в качестве датчика применяется механический прерыватель илииндуктивный датчик (бесконтактный датчик) или энкодер.

Электронные счетчики импульсов могут иметь высокую степень защиты IP (степень защиты оболочки) от пыли и воды (например, IP65).

Счетчик импульсов (некоторые модели) может иметь встроенную функцию тахометра илирасходомера.

Электронные счетчики импульсов сохраняют результат измерений при исчезновении напряжения питания в течение неограниченного периода времени в энергонезависимой памяти (EEPROM). После возврата напряжения питания счет импульсов продолжается, начиная с сохраненного значения; некоторые модели счетчиков импульсов индицируют факт пропадания напряжения питания во время работы.

Некоторые модели имеют интерфейс для подключения к сети или компьютеру (например, RS485, RS232, CAN), а также аналоговый выход ЦАП, который может быть использован как для передачи информации другим контрольно-измерительным приборам управления исполнительными механизмами (например, электроприводом).

Кроме того, счётчики импульсов классифицируют по направлению счета (режиму работы):

суммирующие счетчики импульсов;

вычитающие счетчики импульсов;

реверсивные счетчики импульсов.

Импульсы от энкодера с определением направления вращения

Реверсивные счетчики импульсов чаще всего используются при работе с 2-х канальнымиэнкодерами или с двумя индуктивными датчиками, при этом:

автоматически счетчиком импульсов определяется направление вращения энкодера;

происходит увеличение в 4 раза разрешающей способности энкодера, то есть 1 полный импульс c энкодера счетчик импульсов превращает в 4 инкремента (см. рис. поясняющий работу счетчика импульсов в реверсивном режиме).

⇐ Предыдущая6Следующая ⇒

RS-триггер

Для формирования сигналов управления триггерами используются часто логические элементы со свойствами триггера Шмитта. Рассмотрим принципиальную схему RS-триггера, которая содержит защелку (транзисторы VT1 и VT2), а также два раздельных статических входа управления (транзисторы VТЗ и VТ4). Эти входы управления называются R (reset — сброс) и S (set — установка). Иногда входы R и S называют по-другому: clear — очистка (сброс) и ргезеt — предварительная установка соответственно. Ко входам раздельного статического запуска триггера К и S присоединены управляющий переключатели S1 и S2. Поскольку от каждого из них на входы моЖНо подать напряжение низкого Н или высокого В уровней, то имеется четыре комбинации этих управляющих сигналов. Они перечислены в колонках R и S таблицы состояний RS-триггера. Если от S1 и S2 подать на оба входа R и S напряжение низкого уровня (Н, Н), то транзисторы VТЗ и VT4 открывающих токов не получат будут разомкнуты и поэтому не смогут повлиять на состояние транзисторов защелки VT1 и VT2. Напряжения на выходах триггера Q и Q останутся без изменения. Это значит, что в триггере осталась информация, записанная ранее.

Переведем движок переключателя S2 в положение В (высокое входное напряжение), оставив S1 в Н (низкое). Теперь транзистор VT4 будет насыщен, он замкнется и окажется низким. напряжением на коллекторе присоединенного в параллель ему транзистора VT2. На входе Q, будет также напряжение низкого уровня. Транзистор VT1 больше не получит от выхода Q открывающий базовый ток, поэтому он перейдет в состояние отсечки. По этой причине на выходе Q появляется напряжение высокого уровня (транзистор VT3 от переключателя Sl ток смещения не получает и нз этот процесс в триггере не влияет). Данное со. стояние транзисторов УТ1 и VT2 будет зафиксировано, защелкнуто.

Поменять напряжения на выходах Q и Q можно, если перевести движки переключателей S и S2 в положения В и Н соответственно (третья строка таблицы). Наконец, возможно четвертое состояние переключателей S1 и S2: оба их движка переводятся в состояние В. Такой входной сигнал RS-триггер зафиксировать не может. Действительно, в этом случае, когда S1 = S2 = В, на обоих выходах Q и Q должно появиться напряжение низкого уровня. Но если S1 и S2 строго одновременно отсоединить от входов, триггер переключится в неопределенное состояние. Иначе, после исчезновения входного состояния В, В защелка не переключается однозначно. Таким образом, два логических уровня В, В одновременно на входы R и S подавать нельзя.

На риснке показано функциональное обозначение RS-триггера, составленного из двух двухвходовых инверторов. Такой триггер можно строить на элементах И и на элементах ИЛИ. В таблице приведены логические состояния RS-триггеров, построенных на элементах И и ИЛИ. Строки состояний “без изменений” и “неопределенность” здесь меняются местами в зависимости от выбранного соответствия 1 и О напряжениям высокого и низкого уровня.

Таким образом, RS-триггер имеет два раздельных статических входа управления, чтобы можно было записывать и хранить 1 бит информации. Вместе с тем, известно, что триггерные ячейки — это основа многих динамических устройств, главные из которых: делители частоты, счетчики и регистры. В этих устройствах записанную ранее информацию по специальному сигналу, называемому тактовым, следует передать на выход и переписать в следующую ячейку. Для осуществления такого режима RS-триггер необходимо снабдить тактовым входом C(clock).

Вход

Выход

R

S

Q

Q

Н

Н

Без изменений

Н

В

В

Н

В

Н

Н

В

Н

Н

Неопределённо

Вход

Выход

R

S

Логика И

Логика ИЛИ

Q

Q

Q

Q

Неопределённо

Без изменений

1

1

1

1

1

1

1

1

Без изменений

Неопределённо

Регистры на триггерах

RS-триггер способен сохранять 1 бит цифровой информации. Если необходимо хранить несколько бит, например, цифровое двоичное слово из нескольких двоичных разрядов (в микроконтроллерах обычно 8 или 16), то триггеры могут соединяться параллельно, образуя регистры. Это простейшие устройства для временного хранения набора двоичных цифровых разрядов, в которых каждый триггер сохраняет значение одного разряда (0 или 1. т. е. один бит). Так, показанный ниже 4-разрядный регистр на RS-триггерах содержит четыре отдельных триггера.

Любое двоичное число от (0000)2 до (1111)2 может быть сохранено в этом регистре просто путем установки или сброса соответствующего триггера. Давайте предположим, что первый триггер установлен (Q1 = 1), второй сброшен (Q2 = 0), третий также сброшен (Q3 = 0), а четвертый установлен (Q4 = 1). Тогда двоичное число, записанное в регистр, будет (1001)2.

Кроме параллельных регистров, предназначенных для хранения цифровых слов, на RS-триггерах делаются и так называемые регистры сдвига, в которых разряды цифрового слова последовательно с приходом каждого тактового импульса сдвигаются влево или вправо на один разряд. Схема такого устройства на синхронных триггерах показана ниже.

Подобные регистры находят применение в схемах последовательных интерфейсов, когда поступающие из управляющего контроллера цифровые слова побитно передаются в линию связи.

Метастабильность

Работоспособность триггеров строится на точности перехода от логических параметров 1 и 0. Устройство способно работать в одном состоянии 0 или 1. При этом переход от логических величин осуществляется без задержки в заданное время. Переход зависит от смены напряжения на входах элемента.

Основная проблема устройств кроется в эффекте метастабильности. Это состояние, при котором сигнал попадает на контакт входа в момент перехода из одного состояния в другое. В такие моменты напряжение находится между переходами. Это может привести:

- К полному нарушению работоспособности.

- Несанкционированному включению/выключению цепи.

- Общему нестабильному состоянию.

- Выгоранию ячейки памяти.

Метастабильность можно представить, как шарик, установленный в верхней точке холма. В момент перехода из логического состояния, шарик (напряжение) переходит в одну из сторон согласно схеме. При метастабильности шарик (напряжение) замедляет переход. Этот эффект зависит от шумов цепи, высокого электромагнитного потока и скачков напряжения.

Данный эффект сильно зависим от временного интервала перехода. Также существует погрешность нахождения триггера в состоянии метастабильности. Для снижения данного эффекта инженеры вносят в схему 2 устройства, подключенных параллельно. Такая цепь позволяет снизить возможность появления метастабильности, уменьшить время нахождения цепи в этом состоянии. Так же 2 триггера в цепи значительно увеличивают время перехода, снижают зависимость от частотных и электромагнитных влияний.